PCB疊層設(shè)計(jì),其實(shí)和做漢堡有類似的工藝。漢堡店會(huì)精心準(zhǔn)備每一層漢堡,就像PCB廠家的PCB板層疊在一起一樣。漢堡會(huì)有不同的大小和形狀,有各種各樣的配料,秘密醬汁覆蓋著我們自己的烤面包。就像我們?cè)赑CB上使用不同類型的金屬芯一樣,我們也會(huì)提供各種各樣的餡餅。

現(xiàn)在你可能想知道我們是如何制造世界上最好的電路板的。讓我來告訴你我們的秘密,這都是關(guān)于PCB堆棧的。堆垛是PCB設(shè)計(jì)和制造過程中的重要組成部分。良好的堆疊設(shè)計(jì)是減少電子線路電磁輻射的關(guān)鍵。從而提高了電路板的整體信號(hào)完整性。另一方面,一個(gè)糟糕的堆疊設(shè)計(jì)可能導(dǎo)致更高的電磁發(fā)射和信號(hào)損失。每個(gè)PCB設(shè)計(jì)者的工作必須包括減少由差模噪聲和共模發(fā)射引起的PCB回路的電磁發(fā)射。

現(xiàn)代電子學(xué)圍繞著電子組件的小型化。在電子制造商中,有一種廣泛流行的趨勢(shì),就是把更多的處理能力封裝到一個(gè)小的封裝中。嚴(yán)格地說,從電子學(xué)的角度來說,外形尺寸越小越好。業(yè)內(nèi)專家預(yù)測(cè),我們不久將達(dá)到晶體管級(jí)電子元件的物理極限。盡管如此,我們相信一個(gè)PCB設(shè)計(jì)師可以在設(shè)計(jì)層面創(chuàng)造奇跡,在我們這樣的專家制造商的幫助下,使PCB更小、更致密。

通常被忽略的是,理解HDI疊層和標(biāo)準(zhǔn)疊層之間的差異非常重要. 主要原因是與HDI堆疊技術(shù)相關(guān)的一長(zhǎng)串優(yōu)勢(shì),包括每平方英寸的組件密度更高、縱橫比更低以及與標(biāo)準(zhǔn)堆疊相比更少的層數(shù)。

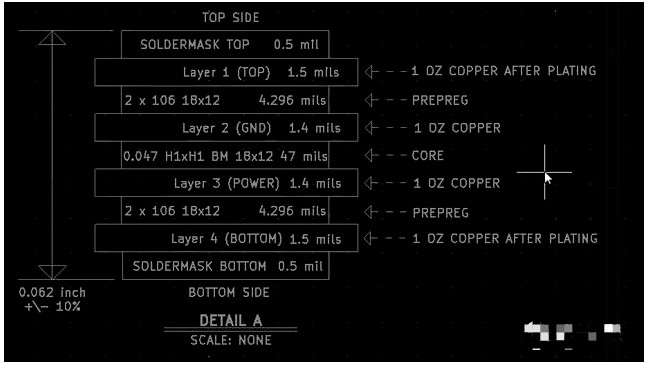

標(biāo)準(zhǔn)疊層設(shè)計(jì)取決于信號(hào)層的數(shù)量。對(duì)于標(biāo)準(zhǔn)PCB疊層,關(guān)鍵參數(shù)包括層數(shù)、接地和電源平面數(shù)、電路頻率、層順序和發(fā)射要求。一些附加參數(shù)包括層與屏蔽或非屏蔽外殼之間的間距。

標(biāo)準(zhǔn)疊層的關(guān)鍵設(shè)計(jì)規(guī)則包括保持信號(hào)層之間的空間和使用大的核心來避免EMC問題。值得一提的是,標(biāo)準(zhǔn)疊層的主要優(yōu)點(diǎn)是外層的平面對(duì)內(nèi)層進(jìn)行屏蔽。然而,主要的缺點(diǎn)包括由于存在元件安裝焊盤,特別是在高密度PCB上,接地層的減少。

HDI疊層技術(shù)是一種前沿技術(shù),正在革新多層PCB的設(shè)計(jì)和制造。HDI為疊層提供了一個(gè)順序構(gòu)建,因此允許有更多的設(shè)計(jì)選擇。HDI簡(jiǎn)化了復(fù)雜電路板的設(shè)計(jì)架構(gòu)。此外,HDI疊層使用盲孔和埋孔,以及疊層和交錯(cuò)過孔。與標(biāo)準(zhǔn)疊層相比,HDI疊層架構(gòu)遵循一種稍微不同的方法。球的層數(shù)由球的層數(shù)決定。影響疊加的其他因素包括信號(hào)層的數(shù)量、電源層和地面層的數(shù)量。

此外,建議HDI疊層的平面和信號(hào)層的數(shù)量應(yīng)為奇數(shù)或偶數(shù)(兩者均為偶數(shù)對(duì)于平衡結(jié)構(gòu)來說是最好的)。這些層應(yīng)該對(duì)稱放置。微孔結(jié)構(gòu)對(duì)制造過程有很大的影響,因?yàn)樗鼈冎苯佑绊憣訅貉h(huán)的次數(shù),而與標(biāo)準(zhǔn)疊層不同。當(dāng)然,HDI不需要復(fù)雜的體系結(jié)構(gòu)。設(shè)計(jì)人員最常犯的錯(cuò)誤之一就是創(chuàng)建不必要的復(fù)雜架構(gòu)。

目前市面上有一些HDI疊層規(guī)劃工具。疊層規(guī)劃工具將確保HDI印刷電路板設(shè)計(jì)將在第一時(shí)間制造出來。工具創(chuàng)建了技術(shù)級(jí)別類別,讓您更好地了解不同軌跡和不同通孔尺寸所需的技術(shù)復(fù)雜程度。因?yàn)楦呙芏?u>集成電路板值得額外的成本,可以試試免費(fèi)的工具:HDI Stackup Planner!

HDI疊層架構(gòu)根據(jù)板層的數(shù)量和HDI板的順序?qū)訅憾譃榀B層類。這些等級(jí)由公式X-N-X確定,其中X是電路板兩側(cè)所需的層壓數(shù)量,N是信號(hào)層的數(shù)量。必須指出的是,隨著對(duì)順序?qū)訅阂蟮脑黾樱宓膬r(jià)格將上漲。

因此,利用激光鉆頭制造的單層層壓將更為有利可圖。在以最便宜的方式利用微氣孔方面,這個(gè)堆棧類是一個(gè)無需考慮的問題。使用激光鉆將允許設(shè)計(jì)者實(shí)現(xiàn)更小的焊盤和通孔尺寸。這有助于減輕一些設(shè)計(jì)限制并減少設(shè)計(jì)時(shí)間。

在微通孔開始和停止的層上的變化越多,PCB制造所需的順序?qū)訅壕驮蕉唷H魏我粋€(gè)微孔開始或停止的層都需要一個(gè)子結(jié)構(gòu),每個(gè)子結(jié)構(gòu)都需要一個(gè)額外的層壓周期。(層壓工藝被定義為在兩個(gè)相鄰的銅層之間通過加熱和加壓將一組帶有未固化電介質(zhì)的銅層壓制成多層PCB層壓板)。

0-N-0疊加

電路板的成本和復(fù)雜性隨著與堆疊相關(guān)的工藝步驟的增加而增加。額外的制造過程也意味著更多的產(chǎn)量損失。N表示第一層或基礎(chǔ)層壓(或芯層疊層)中的層數(shù),0表示沒有順序?qū)訅翰襟E,也沒有額外的電介質(zhì)層和銅層。下面是一個(gè)0-N-0疊加的例子。

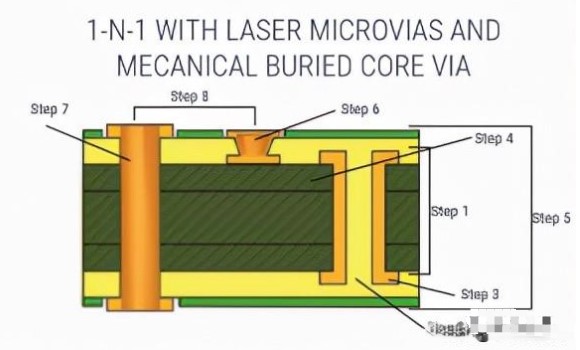

1-N-1疊加

堆芯1-1上的順序?qū)訅?-1的任意一側(cè)。一個(gè)連續(xù)層壓增加了兩個(gè)銅層,總共N+2層。這種堆疊設(shè)計(jì)沒有堆疊過孔。有一個(gè)額外的層壓沒有堆疊過孔。埋在地下的通孔是用機(jī)械鉆的。通孔無需使用導(dǎo)電填料。它將自然填充介電材料。第二層層壓增加了頂層和底層。然后,我們用最后一個(gè)機(jī)械鉆完成。以下是1-N-1疊加的步驟,

板芯是層壓的。(核心只能是兩層,所以沒有層壓。)

板芯采用機(jī)械鉆孔。

機(jī)械鉆是電鍍的。

第二層被成像/蝕刻。

順序?qū)訅涸黾恿藘蓚€(gè)額外的層。(機(jī)械鉆現(xiàn)在是一個(gè)埋孔。)

形成激光鉆孔。

形成最終的通孔。

激光鉆孔和通孔是電鍍的。

PCB制造商計(jì)劃在第1層和第2層之間添加適量的預(yù)浸料,以便樹脂流入埋入的通孔中。

無論是HDI還是標(biāo)準(zhǔn)的堆疊板,遵循一定的指導(dǎo)原則,根據(jù)應(yīng)用和它的要求是實(shí)現(xiàn)PCB堆疊設(shè)計(jì)的最佳可能方式。我們列出了一些指導(dǎo)原則,以幫助您實(shí)現(xiàn)可能的PCB堆疊設(shè)計(jì),

PCB堆疊取決于設(shè)計(jì)中存在的信號(hào)層數(shù)量。信號(hào)層隨PCB的應(yīng)用而變化。例如,與低速信號(hào)電平相比,高速信號(hào)或大功率應(yīng)用可能需要更多的層。

低螺距高引腳數(shù)的復(fù)雜器件,如bga,通常需要更多的信號(hào)層。信號(hào)完整性要求(如極低串?dāng)_)也可能導(dǎo)致信號(hào)層數(shù)量增加。

混合信號(hào)類型-大量模擬信號(hào)和數(shù)字信號(hào)將需要在這兩種類型之間進(jìn)行分離,并可能增加信號(hào)層的數(shù)量。

地面和電源平面的使用允許設(shè)計(jì)者純粹為信號(hào)路由分配信號(hào)層;它們還降低了電源和接地軌中的直流電阻,從而確保設(shè)備上的直流電壓降更小。

接地層是PCB中連接到電源接地連接的銅平面。電源層是連接到電源軌的PCB中的一個(gè)銅平面。

這些平面還為時(shí)變和高頻信號(hào)提供信號(hào)返回路徑,并有助于顯著降低噪聲和信號(hào)串?dāng)_,從而提高信號(hào)完整性。功率平面還提高了PCB電路的電容去耦能力。飛機(jī)還通過減少電磁輻射來提高電磁兼容性能。

也可以閱讀我們的文章:PCB電源設(shè)計(jì)的7個(gè)注意事項(xiàng)

受控阻抗是由PCB跡線及其相關(guān)參考平面形成的傳輸線的特征阻抗。當(dāng)高頻信號(hào)在PCB傳輸線上傳播時(shí),它是相關(guān)的。均勻的控制阻抗對(duì)于實(shí)現(xiàn)良好的信號(hào)完整性非常重要,即信號(hào)的傳播沒有明顯的失真。

也可以閱讀我們的文章指定控制阻抗要求 .

當(dāng)基準(zhǔn)面不是下一層時(shí),下一層上的另一個(gè)銅特征有可能成為基準(zhǔn)。

從制造業(yè)的角度來看,我們需要保持統(tǒng)一蝕刻橫穿直線的長(zhǎng)度,既有寬度又有梯形的影響。這就是蝕刻公差和均勻性的原因。

D)順序?qū)优帕?/p>

堆棧設(shè)計(jì)的另一個(gè)關(guān)鍵方面是順序?qū)优帕小8鶕?jù)微帶線的厚度來安排高速信號(hào)層是設(shè)計(jì)者在布線前必須考慮的關(guān)鍵參數(shù)之一。將信號(hào)層放置在電源平面下方將允許緊密耦合。

對(duì)于精確的層布置,電源和地平面之間保持最小距離。其他關(guān)鍵參數(shù)包括避免相鄰放置兩個(gè)信號(hào)層,以及建立頂層和底層的對(duì)稱堆棧。

在順序?qū)訅褐校M量限制層壓步驟的數(shù)量,因?yàn)樗兊酶影嘿F和耗時(shí)。

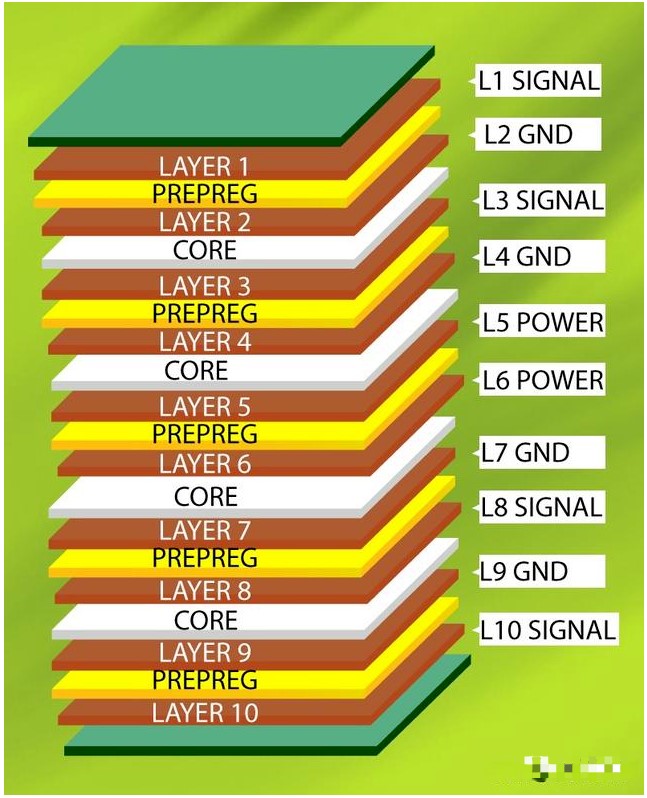

典型的10層疊層,每個(gè)信號(hào)層有地面層

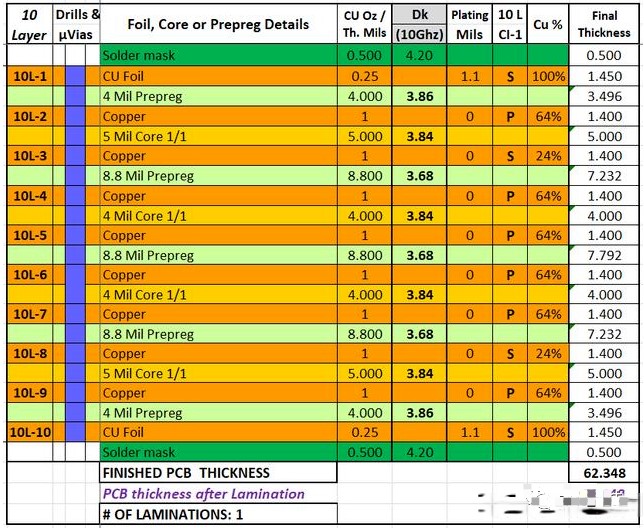

另一個(gè)10層疊層的例子

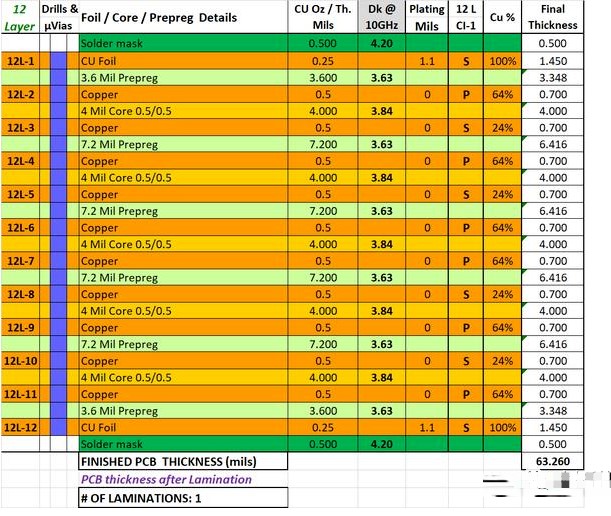

一個(gè)12層PCB疊層的例子

e-CAD工具的PCB疊層截圖