MOSFET也叫金屬-氧化物半導體場效應晶體管,簡稱金氧半場效晶體管,是一種可以廣泛使用在模擬電路與數字電路的場效晶體管。MOSFET依照其“通道”的極性不同,可分為“N型”與“P型” 的兩種類型,通常又稱為NMOSFET與PMOSFET,簡稱包括NMOS、PMOS等。本文帶大家熟悉一下MOSFET的結構和前景。

MOSFET的結構

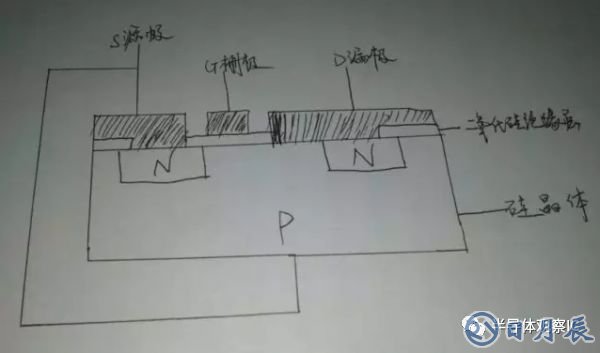

上圖是典型平面N溝道增強型NMOSFET的剖面圖。它用一塊P型硅半導體材料作襯底,在其面上擴散了兩個N型區,再在上面覆蓋一層二氧化硅(SiO2)絕緣層,最后在N區上方用腐蝕的方法做成兩個孔,用金屬化的方法分別在絕緣層上及兩個孔內做成三個電極:G(柵極)、S(源極)及D(漏極)。

從圖中可以看出柵極G與漏極D及源極S是絕緣的,D與S之間有兩個PN結。一般情況下,襯底與源極在內部連接在一起,這樣,相當于D與S之間有一個PN結。

圖1是常見的N溝道增強型MOSFET的基本結構圖。為了改善某些參數的特性,如提高工作電流、提高工作電壓、降低導通電阻、提高開關特性等有不同的結構及工藝,構成所謂VMOS、DMOS、TMOS等結構。

MOSFET重點參數

MOSFET的參數很多,包括直流參數、交流參數和極限參數,但一般使用時關注以下主要參數:

1、IDSS—飽和漏源電流。是指結型或耗盡型絕緣柵場效應管中,柵極電壓UGS=0時的漏源電流。

2、UP—夾斷電壓。是指結型或耗盡型絕緣柵場效應管中,使漏源間剛截止時的柵極電壓。

3、UT—開啟電壓。是指增強型絕緣柵場效管中,使漏源間剛導通時的柵極電壓。

4、gM—跨導。是表示柵源電壓UGS—對漏極電流ID的控制能力,即漏極電流ID變化量與柵源電壓UGS變化量的比值。gM是衡量場效應管放大能力的重要參數。

5、BUDS—漏源擊穿電壓。是指柵源電壓UGS一定時,場效應管正常工作所能承受的最大漏源電壓。這是一項極限參數,加在場效應管上的工作電壓必須小于BUDS。

6、PDSM—最大耗散功率。也是一項極限參數,是指場效應管性能不變壞時所允許的最大漏源耗散功率。使用時,場效應管實際功耗應小于PDSM并留有一定余量。

7、IDSM—最大漏源電流。是一項極限參數,是指場效應管正常工作時,漏源間所允許通過的最大電流。場效應管的工作電流不應超過IDSM 。

MOSFET的市場前景

微處理器運算效能不斷提升,帶給深入研發新一代MOSFET更多的動力,這也使得MOSFET本身的操作速度越來越快,幾乎成為各種半導體主動元件中最快的一種。MOSFET在數字信號處理上最主要的成功來自CMOS邏輯電路的發明,這種結構最大的好處是理論上不會有靜態的功率損耗,只有在邏輯門的切換動作時才有電流通過。CMOS邏輯門最基本的成員是CMOS反相器,而所有CMOS邏輯門的基本操作都如同反相器一樣,在邏輯轉換的瞬間同一時間內必定只有一種晶體管處在導通的狀態下,另一種必定是截止狀態,這使得從電源端到接地端不會有直接導通的路徑,大量節省了電流或功率的消耗,也降低了集成電路的發熱量。

MOSFET在數字電路上應用的另外一大優勢是對直流信號而言,MOSFET的柵極端阻抗為無限大,也就是理論上不會有電流從MOSFET的柵極端流向電路里的接地點,而是完全由電壓控制柵極的形式。這讓MOSFET和他們最主要的競爭對手BJT相較之下更為省電,而且也更易于驅動。

在CMOS邏輯電路里,除了負責驅動芯片外負載的驅動器外,每一級的邏輯門都只要面對同樣是MOSFET的柵極,如此一來較不需考慮邏輯門本身的驅動力。相較之下,BJT的邏輯電路就沒有這些優勢。MOSFET的柵極輸入電阻無限大對于電路設計工程師而言亦有其他優點,例如較不需考慮邏輯門輸出端的負載效應。