通過基于軟件的防火墻部署網絡安全的傳統方法,由于無法滿足時延與帶寬需求而無法擴展。將賽靈思自適應器件的靈活性及可配置性及其 IP 和工具產品相結合,能夠顯著提高安全處理性能。

概要

本白皮書探討了多種防火墻架構,其中包括基于軟件與 NPU 的架構,并且闡明了為什么新一代設計需要基于賽靈思自適應器件的內聯防火墻架構。賽靈思 16nm?FPGA?與 SoC以 及 7nm Versal?ACAP 能夠以硬化塊與軟 IP 的形式提供多種架構組件,因此使其成為設計新一代安全設備的理想選擇。 這些 IP 包括高速 SerDes 和多速率接口?IP,例如硬化 MAC、PCIe ?接口與存儲器控制器。 此外,賽靈思器件還可以提供具備流分類軟搜索 IP 的業界一流存儲器架構,使其成為網絡安全和防火墻應用的最佳選擇。

介紹

本白皮書介紹了在企業與電信數據中心網絡中用作新一代防火墻 (NGFW) 的安全設備的功能、部署與架構。賽靈思器件的靈活性與可配置性與其 IP 與工具產品相結合,能夠顯著提高用于威脅檢測與預防的網絡安全設備的性能,同時可以實現性能擴展。此外,這些器件還可以助力實現即將面世的新一代安全技術,例如后量子加密 (PQC) 以及用于異常檢測的機器學習?(ML) 技術。

由于企業網絡正在向基于策略與意圖的網絡轉型,因此流與策略可以定義有關流量的操作(路由、QoS、拋棄、標記等)。此外,輸入流量所需的安全策略會根據網絡中流的性質不斷變化。大多數流量需要根據狀態以動態方式處理網絡流量。

基于端口的傳統防火墻可以提供基于邊界的保護,它可以根據數據包參數(如:IP 地址與 TCP/UDP 端口號)過濾流量,因為應用感知僅在軟件中進行處理,其無法進行性能擴展。NGFW 應當不但能夠識別和處理特定類別的流量,而且還應當能夠識別與應用內容相關的威脅。企業使用的眾多應用允許端口跳變,采用非標準端口或者隱藏 SSL 隧道中的威脅,因此傳統的基于靜態端口的防火墻無法檢測出威脅與惡意軟件。

企業網絡防火墻

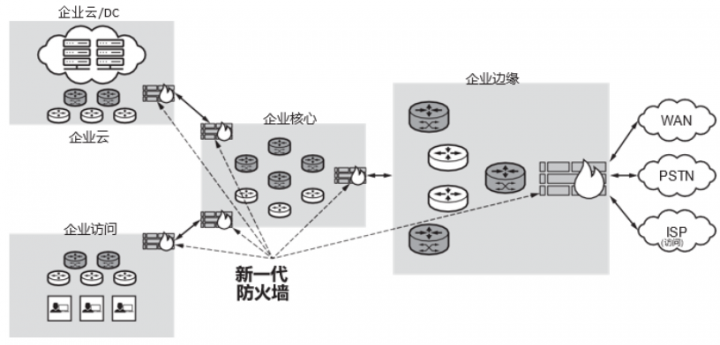

為確保企業辦公室之間的安全性,歷代網絡防火墻都部署在網絡邊緣,其聯網絡采用多種傳輸網技術,而且往往會采用同一個網絡流水線作為公共網。隨著基于策略的網絡的演進發展以及軟件定義網絡 (SDN) 與基于意圖的網絡 (IBN) 的涌現,具有不同吞吐量與功能的防火墻在逐步部署到企業網絡的眾多不同位置。參見圖 1。

圖 1: 企業網絡的新一代防火墻

如圖 1所示,防火墻的作用已經從企業網邊界擴展到企業中的多個位置,如:連接企業總部與分支機構,保護連接邊緣,或保護企業數據中心的流量不受企業訪問的影響。NGFW 能夠根據多種數據包參數(端口、 IP 地址、有效載荷內容)或者根據 L3-VPN 或 SSL/TLS 等加密技術檢測和阻止網段之間的威脅與惡意軟件。

防火墻部署與功能

安全設備負責檢查和分析來自企業網絡外部的所有流量。防火墻能夠部署到企業網絡的多個位置,如:企業不同部門之間的流量,或者通過由交換機和路由器組成的多個網絡節點從企業訪問進入企業數據中心的流量。

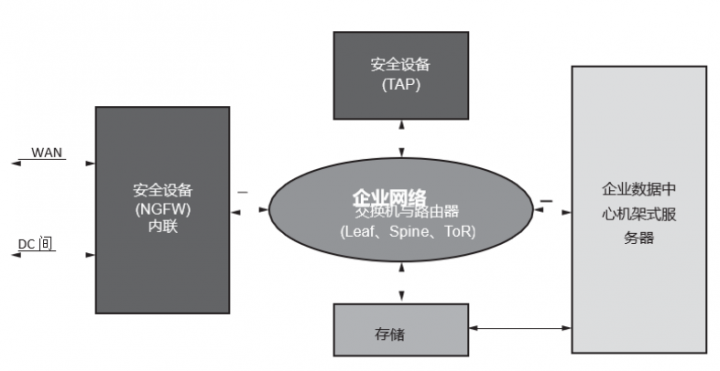

安全設備 (NGFW) 可以內聯部署,也能夠以旁路模式部署。這兩種模式的主要區別是內聯模式直接連接到外部網絡端口,而旁路設備可以連接到交換機或路由器的分流器或鏡像端口。圖 2 顯示了網絡中的防火墻連接。雖然防火墻的功能大同小異,但是內聯防火墻比旁路防火墻設備更復雜,同時性能也更強大。

部署到具體位置的防火墻的規模與功能在策略規則分配方面有所不同,但是某些基本功能(如:流量分類、緩沖等)保持不變。

圖 2: 企業的絡中的 NGFW

網絡節點或安全設備可以負責實現以下安全功能:

1. L2 安全 - 用于鏈路加密的 MACSec

2. L3 安全 - 來自用戶與其他網絡節點的 VPN 隧道

3. 無效流量的阻斷與過濾(基于協議與端口的過濾)

4. 傳入與傳流量的 TLS/SSL 加密/解密

5. 跨多個流量的異常檢測

6. 狀態模式匹配

7. 統計異常檢測

8. IP 分片

9. TCP 重組與排序

10. 基于正則表達式 (regex) 的簽名/內容匹配

除了上述功能之外,新一代網絡安全產品也已經開始實現用于網絡分析與惡意軟件預測的 ML 模型。此類模型不依賴基于簽名的傳統檢測功能。支持ML的防火墻可以收集遙測數據,而且可以在威脅出現之前提前部署安全策略。

上述功能的其中一部分是基本功能,是所有網絡節點(安全交換機與路由器)的組成部分,而且是在采用?ASIC?或可編程器件創建的已部署網絡交換機和路由器中實現;其他功能(L3 及更高級功能)更加復雜,需要大量流量分類與處理操作。網絡協議層越高,流量處理的復雜性就越高。例如,層1(L1) 安全只需要幀級加密(如:OTN 傳輸有效載荷幀),而且是采用批量加密協議 (AES-GCM) 在光網絡節點中實現。層 2(L2) 與層 3(L3) 需要在以太網與 IP 層面進行數據包處理,其需要數據包級別的處理。層 4(L4) 與更高級別需要進行內容級安全處理,其中每個 TCP 或 UDP 會話都包括多個以太網與 IP 數據包。一些L2 與 L3 安全功能可以在硬件器件(ASIC、ASSP、FPGA、SoC、ACAP 與 NPU)中輕松實現。此外,更高層的安全處理(L3 及以上)也需要對傳入流量進行基于軟件的內容處理,才能實現威脅檢測與清除。

由于新的接入網技術(5G?前傳、PON 與電纜)在過去幾年已經大幅提高了吞吐量與流量,因此僅僅基于軟件流量處理的防火墻設備不足以滿足預期吞吐量下的性能與時延要求。

新一代防火墻的硬件架構

由于防火墻需要處理和檢查所有的傳入流量,因此它們需要執行以下操作:

·L2/L3 數據包處理

·L2/L3 安全功能

·L4–L7 數據包處理與安全

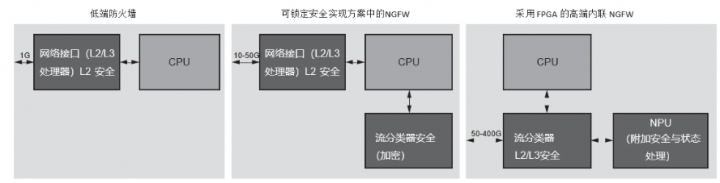

圖 3 顯示為防火墻設計選項。

圖 3:防火墻的演進發展:旁路與內聯處理對比

低端防火墻設備(通常低于 10G)的設計可以采用網絡接口器件與?CPU。常見的網絡接口 (NIC) 器件(定制 ASIC、FPGA 或 ASSP)可以處理處理理傳入流量(以太網與 IP 數據包),并且能夠執行眾所周知的 L2 與 L3 功能,而更高層 (L4–L7)功能是由在 CPU 中運行的軟件執行。

中端防火墻能夠處理更高的吞吐量 (10G–50G),其設計主要采用網絡接口器件與旁路安全處理器(安全 ASIC、NPU 或 FPGA)。由于只使用軟件的解決方案不能以更高的吞吐量對流量進行分類和處理,因此旁路安全處理器可以用作 CPU 協處理器,以便卸載加密/解密、公開密鑰基礎設施(PKI)和/或狀態流量處理功能。雖然在這種架構中可以將 ASIC 或 NPU 用作網絡接口,但是在中端防火墻中采用 FPGA 日漸流行,因為它在內聯模式下可以實現處理傳入流量所需的可擴展性和靈活性,從而可以降低威脅檢測與預防方面的時延。

吞吐量達到 50G-400G 的新一代高端防火墻主要設計用于內聯操作模式。在內聯模式下,網絡接口器件需要更加智能,才能處理龐大流量,這涉及到對傳入和傳出數據包的更深入的檢查。此類接口器件也需要實現安全功能,如內聯 IPSec,其采用常用的加密協議與 TCP 級安全。這種架構仍然采用 NPU 來實現具體的加密協議、PKI 和狀態處理。內聯設備的流量分類需求在流量數量與復雜性以及針對高吞吐量流量采取的措施方面各不相同。因此,用于內聯安全處理的可編程器件(如FPGA)是實現此類功能的理想選擇。與 NPU 相比,FPGA 在流量處理方面提供了顯著的時延降低和優異的可擴展性。此外,FPGA 目前還可以配置新一代存儲器接口和片上高帶寬存儲器 (HBM),這對于存儲器密集型流量處理應用非常有用。

將 FPGA 用作網絡安全的流量處理器

進出安全設備(防火墻)的流量進行多級別加密。L2 加密/解密 (MACSec) 是在鏈路層 (L2) 網絡節點(交換機與路由器)進行處理。超出 L2(MAC 層)的處理通常包括更深層的解析、L3 隧道解密 (IPSec) 以及加密 SSL 流量與 TCP/UDP 流量的處理。數據包處理涉及傳入數據包的解析與分類以及高吞吐量 (25–400Gb/s) 的龐大流量 (1–20M) 的處理。由于需要大量計算資源(核心),NPU 可以用于相對更高速率的數據包處理,但是無法實現低時延、高性能可擴展流量處理,因為流量處理采用?MIPS/RISC?核心,而根據其可用性來調度此類核心難度很大。采用基于FPGA的安全設備可以有效消除基于 CPU 和 NPU 的架構所帶來的上述限制。

安全設備的流量處理

流量處理是數據包處理的更高級別的抽象,因為一個數據流是由類型相似的眾多數據包組成。流量處理包括以下主要組成部分:

·數據包解析

·數據包查找

·數據包編輯

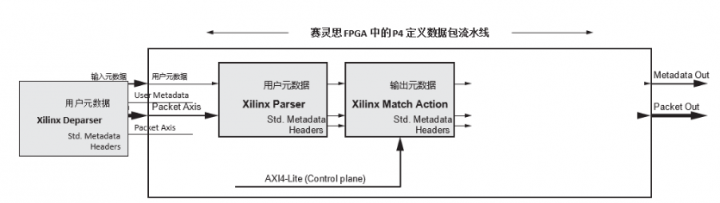

賽靈思提供了采用高級抽象語言 P4 進行數據包處理的工具,其可以實現數據包解析、分類、查找與數據包編輯功能。與基于 RTL 語言的實現相比,使用 P4 完成數據包處理可以在更高的抽象層實現。采用P4可以提高現有可編程FPGA架構的靈活性,因為它可以輕松實現數據包解析、數據包編輯以及流量表條目的修改。

如圖 4 所示,P4 介紹可以采用 P4 編譯器編譯的并且映射在賽靈思 FPGA 中的數據包處理流水線架構,其中采用了基本架構組件。P4 語言定義數據包解析、查找(IPv4、IPv6 和其他數據包字段)以及數據包的編輯(逆解析)。P4定義的架構可以直接應用于安全處理流水線,如:IPSec安全關聯 (SA)、安全策略 (SP) 查找以及進/出流量的隧道處理實現。

圖 4: 基于 P4 的數據包處理流量分類與查找

數據包處理的三個主要組成部分包括:

數據包解析:來自多個應用,訪問企業網絡與數據中心網絡不同節點所產生的流量需要針對具體流量類型分類。解析過程涉及眾多數據包參數的提取,其中包括 L2 包頭、L3 包頭以及來自數據包已知偏移量的字段。這些解析需求隨應用不同以及數據包不同位置的簽名不同而變化。FPGA 的靈活架構加上 P4 定義的解析器能夠滿足這些不斷變化的分類需求。

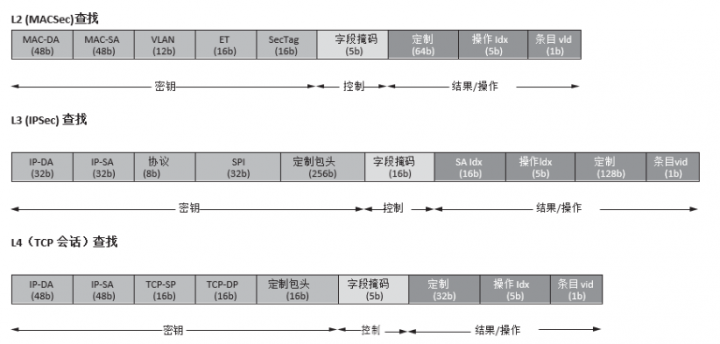

數據包查找:完成解析之后,需要根據流量的類型對數據包進行分類。加密的數據包根據協議與安全包頭字段進行解密處理。匹配操作模塊對數據包解析器模塊生成的搜索密鑰進行查找,以實現目的地/操作分配。對于加密流量,秘鑰搜索包括安全關聯與安全策略的確定,它可以決定應用于加密數據包的解密密鑰信息和策略。L2 加密數據包 (MACSec) 需要更簡單直接的查找,而更高層的加密查找可能更加復雜,具有更寬泛的密鑰與結果值。圖5 介紹了 MACSec、IPSec 和 TCP 協議的查找示例。查找次數隨網絡節點變化,不過某些情況下一些流量類別需要多層查找。

圖 5: L2/L3/L4 安全實現方案查找示例

上述查找特定于安全處理。此外,防火墻也可以針對路由器功能、網絡地址轉換 (NAT) 以及傳入流量的策略(或訪問控制)查找實現附加查找。

以下安全與網絡查找類別包括精確匹配、最長前綴匹配 (LPM) 和通配符搜索,其采用由包頭字段組成的密鑰:

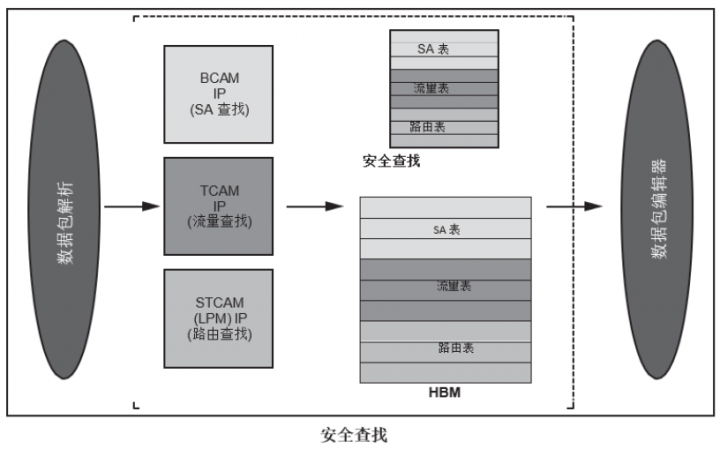

如圖 6 所示,數據包處理查找可分為三類,有各自的表和密鑰大小要求。

圖 6: 采用基于 FPGA 的安全設備進行查找

賽靈思的 IP 產品組合包括用于二進制匹配、通配符三元匹配和最長前綴匹配的搜索 IP。這些搜索 IP 可以靈活組合,以適應所有采用片上 SRAM?與?DRAM?(HBM) 的賽靈思 FPGA。這三類搜索 IP 全部支持 100Mb/s 至 400Gb/s 吞吐量。

秘鑰寬度、結果寬度和表內的條目數量可以決定 FPGA 所用片上邏輯資源和存儲器 (SRAM/DRAM) 的數量。由于賽靈思擁有具有不同資源(邏輯/存儲器)數量的廣泛器件類別,因此用戶能夠針對其吞吐量與表大小要求選擇具有適當資源的賽靈思器件。此外,查找 IP 配備用于修改和更新流量表條目的應用層軟件 API。

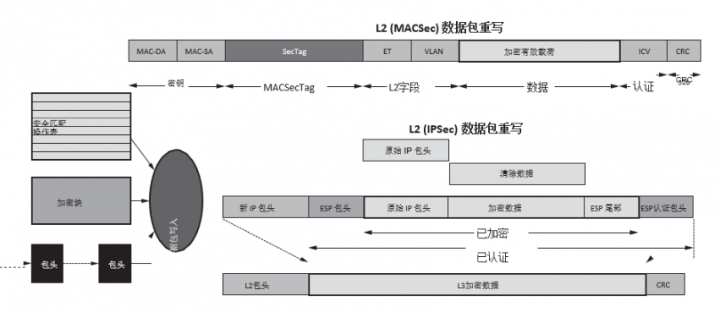

數據包編輯:安全處理涉及在完成解析、包頭查找和過濾之后將修改后的加密或解密數據包發送到出站端口。傳出流量包括修改后的新包頭、更新后的數據包字段、認證包頭以及糾錯字段。部分常見數據包處理需求包括:

圖7 顯示了用于 MACSec 和 IPSec 的數據包編輯/修改操作。在通過出站端口發送數據包之前,可能需要對包頭字段進行多次修改,這包括校驗和與 CRC 的計算與插入。除了標準包頭,數據包通常還包括專用包頭,而且也可能需要采用不同的協議包頭(VXLAN、IP in IP、GRE 等)對數據包進行封裝與解封。賽靈思可編程器件能夠在線路速率下以最大靈活性實現數據包修改。

圖 7:MACSec 與 IPSec 數據包重寫

此外,賽靈思器件還提供 P4 可編程能力,因此也可以采用 P4 實現數據包重寫操作。與 RTL 實現方案相比,P4 逆解析器功能能夠進一步簡化包頭的創建與插入。為在賽靈思器件上以線路速率運行,可以使用賽靈思 P4 編譯器合成?P4 編輯器代碼。

對于應用層安全實現,對數據包重寫操作的需求更加復雜。例如,如果 TCP 數據包在 FPGA 內終止,則會話追蹤與封裝/解封需求會比 IPSec 或 MACSec 數據包修改需求需要更多的邏輯與存儲器資源。

此外,數據包修改任務也可以在軟件(運行 CPU 核心)中執行,但是高端安全設備所需的吞吐量無法通過軟件實現方案滿足線路速率操作。在可編程硬件中執行數據包處理操作的另一個關鍵優勢是可以節省大量的 CPU 資源(CPU 核心),節省下來的資源可以分配給軟件中運行的實際應用。

FPGA 中的應用級安全處理

FPGA 是新一代防火墻內聯安全處理的理想選擇,這是因為采用 FPGA 可以成功滿足對更高性能、靈活性和低時延操作的需求。此外,FPGA 還可以實現應用級安全功能,從而進一步節省計算資源并提高性能。

FPGA 中有關應用安全處理的常見示例包括:

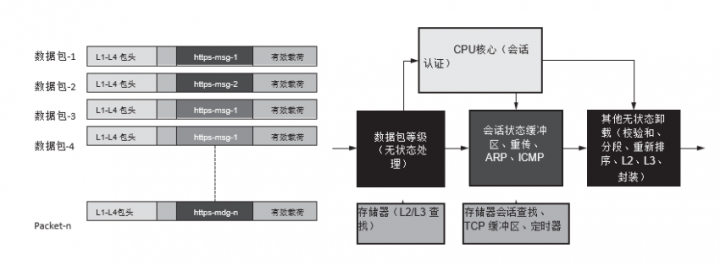

由于眾多用戶空間應用采用 TCP 作為客戶端或服務器模式下的通信協議,并且 TCP 是客戶端與服務器之間的安全 (TLS/SSL) 連接基本塊,因此 TCP 卸載引擎 (TOE) 是用于內聯 FPGA 處理的重要卸載塊。企業防火墻通常同時終止大量 TCP 連接,這將消耗大量的 CPU 周期與存儲器。為了實現應用級安全處理,可能需要采用擁有大量核心的昂貴的高端 CPU 來終止眾多 TCP/UDP 連接。FPGA 中的 TCP 處理實現方案通過節省眾多實現 TOE 所需的內核,能夠顯著節約成本和功耗。

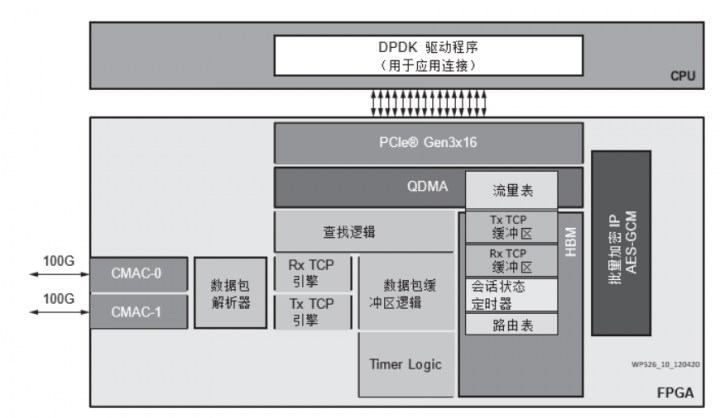

圖 8 顯示了安全設備中由 FPGA 輔助完成數據包處理的示例。由于進入防火墻網絡接口的數據包可能屬于眾多不同的應用,因此追蹤與多個應用關聯的數據包,并將其發送到正確應用或者在正確應用進行接收是一種需要占用大量存儲器的狀態化操作。此外,上述關聯還需要對 TCP 段進進行重新排序、分段和重組。雖然仍然可以采用 CPU 處理協議消息的新連接請求與認證,但是 FPGA 可以追蹤活動會話并且根據會話 ID 將數據包分配給相關應用。

圖 8:采用 FPGA進行應用級狀態處理

FPGA 中的 TLS 卸載/處理

FPGA 的 TLS 處理功能是 TCP 卸載引擎的擴展,其中 TCP 有效載荷的加密與解密在 FPGA 中執行。TSL 會話的發起與認證在軟件中執行(CPU)。在建立安全連接時,由 FPGA 執行后續的 TLS 記錄處理。

圖 9 顯示了在賽靈思器件中作為 CPU 卸載的完整內聯 SSL 處理功能的組件。賽靈思器件可以實現整個邏輯,以處理 100G?以太網接口數據包。它可以識別 TCP 與 TLS 流,并且相應地將數據包引導到相關 CPU 或者采用可編程資源進行處理。

圖 9:FPGA 中的 TLS 卸載

FPGA 中的正則表達式 (Regex)

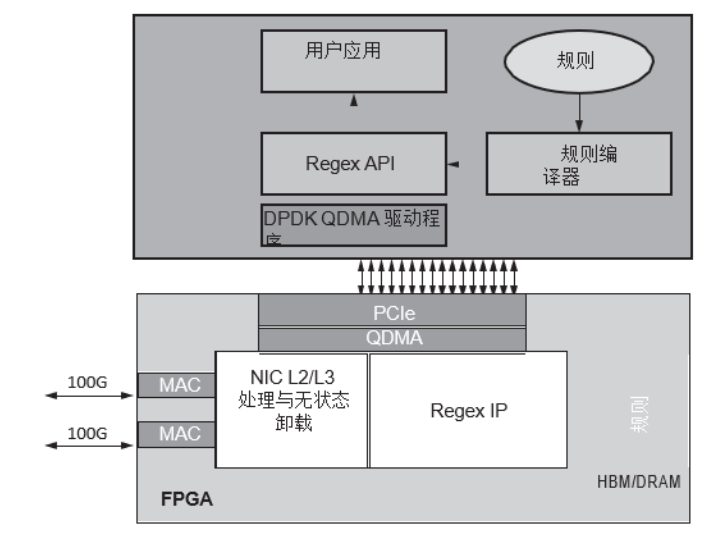

正則表達式 (regex) 涉及流量的有效載荷數據中字符串或特殊字符的匹配。它廣泛應用于 DPI、IPS/IDS、DLP 和 DDoS 防護。Regex 匹配通常是在軟件中執行,其采用專用軟件庫。由于 regex 搜索需要針對眾多規則對有效載荷進行匹配,因此純軟件 regex 處理給新一代安全設備帶來了性能與時延挑戰。

圖 10 說明了采用賽靈思器件的 100Gb/s 內聯 regex 處理。在此 regex 加速處理模型中,Perl 兼容正則表達式 (PCRE) 或 Snort 規則首先在軟件編譯器中進行編譯,然后通過 PCI 接口發送到與 CPU 連接的 FPGA,作為二進制字符串匹配規則條目保存到 FPGA 的內部 SRAM 或DRAM(HBM 或 DDR)存儲器。FPGA 會在內部 SRAM 或 DRAM (片上 HBM 或外部 DDR)中填充大量 regex 規則/條目(轉換成二進制的特殊字符與字的組合)。regex 處理的內聯加速與軟件相比可以顯著提高性能(10-30 倍)。

圖 10:FPGA 中的 Regex 匹配

基于 FPGA 的安全設備中的機器學習 (ML)

在新一代安全設備中,基于 ML 的流量分析與惡意軟件檢測是關鍵應用之一。ML 模型將會被部署用于通過分析加密數據中的特定模式而實現的加密流量檢測。在高端安全設備中,則需要采用 ML 模型處理海量實時數據,以便預測異常,因此采用加速器實現 ML 模型將給高吞吐量與低時延惡意軟件預測帶來巨大優勢。防火墻已經開始在軟件中部署用于異常檢測的 ML 模型。在新一代設備中,賽靈思可編程器件將會通過將 ML 模型卸載到可編程邏輯而提供顯著提高的預測速度。

此類基于 FPGA 的 ML 模型包括:

·隨機樹(隨機森林)

·深度神經網絡?(DNN)

推斷模型的選擇取決于多種因素,如:準確性、輸入模式改變頻率、訓練需求、FPGA 資源利用率等。

賽靈思 ML 解決方案包括支持大多數常用 ML 框架的軟件庫與工具。這些模型可以高效映射到賽靈思可編程器件以及 Versal ACAP 所提供的?AI?引擎中的查找表 (LUT)、DSP?與 SRAM/DRAM 存儲器。

針對 FPGA 中安全分析功能實現 ML 模型的另一個優勢是惡意軟件預測所需要的內聯流量/數據包處理可以在同一個 FPGA 中執行。在 ML 模型的內聯實現方案中,將網絡接口連接到同一個 FPGA 可以節省從 CPU 向 ML 模型發送數據所需的 PCIe? 帶寬。

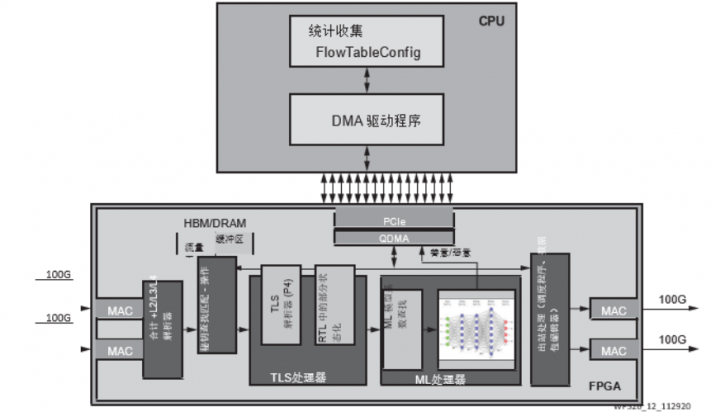

圖 11 顯示了 ML 模型在 200Gb/s 防火墻中的應用。TLS 處理器具有 TSL 解析器以及 IP 數據報中 TLS 參數提取功能。隨后,這些參數反饋給 ML《5018/》 處理器,以便查找和調節 ML 模型的系數。根據相關系數,模型可以預測 TSL 流量的善意與惡意簽名。

圖 11:安全設備中的 ML 模型

采用 FPGA 的新一代安全技術

后量子加密

眾多現有的非對稱算法容易受到量子計算機的破壞。對量子計算安全加密算法的研究和實現已經起步,而已經有學術論文介紹了如何采用 FPGA 實現此類算法。RSA-2K、RSA-4K、ECC-256、DH 和 ECCDH 等非對稱安全算法受到量子計算技術的影響最大。目前正在探討新的非對稱算法實現方案和 NIST 標準化。

目前提議的后量子加密(PQC)包括針對以下方面的環上誤差學習 (R- LWE) 算法:

提議的公共密鑰加密的實現方案包括某些眾所周知的數學運算(TRNG、高斯噪聲采樣器、多項式加法、二進制多項式定標器除法、乘法等)。用于眾多此類算法的 FPGA IP 已經面世或者可以采用 FPGA 構建塊高效實現,如:現有的和新一代賽靈思器件中的 DSP 與 AI 引擎。

安全訪問服務邊緣 (SASE)

安全訪問服務邊緣 (SASE) 是新興的新一代企業安全技術,旨在滿足企業的動態安全訪問需求。SASE 的早期定義在企業邊緣集成自適應網絡與安全需求,其中包括 SD-WAN、軟件與物理防火墻以及網絡安全網關。SASE 需要采用動態安全策略更新來提供對聯網應用的不間斷安全訪問。

采用 FPGA 在硬件中實現 SASE 剛剛起步,不過,由于 FPGA 具有全面的可編程能力,因此它們仍然能夠通過 L2/L3/L4 加密技術和上述其他技術在流量處理以及動態安全連接流水線的提供方面起到重要作用。

用于安全設備的賽靈思工具與 IP

賽靈思器件具有高性能可編程資源以及業界一流的工具與 IP,是設計和實現網絡流量安全處理的理想選擇。它們可以提供最高數據與信號處理能力,以及最新的多速率高吞吐能力。SerDes 用于符合最新接口標準的設計,其中包括 1G-400G 以太網、600G Interlaken 以及高達 400G PCIe 吞吐量。此外,賽靈思器件還提供注冊裸片間路由線路,可支持高達 600MHz 可編程邏輯運算。

除了基本的高性能設計資源,賽靈思還提供用于安全處理的多種設計 IP。這些可編程 IP 包括 MAC 接口、用于向/從主機傳輸數據的高速?DMA、用于流量分類與路由的搜索 IP(BCAM、TCAM 與 STCAM)以及使用 AES-GCM 密碼進行批量加密的片上 HBM 和/或 DDR 存儲器接口與軟加密引擎 (SCE)。

此外,賽靈思還擁有合作伙伴生態系統,其可以提供采用多種密碼協議的批量加密端到端解決方案,以及使用大多數常見密鑰交換(ECCDH、RSA-2K、RSA-4K 等)進行非對稱加密的 IP。除了來自合作伙伴的基礎級標準加密 IP 之外,賽靈思目前還在與合作伙伴合作實現高級 (L4+) 安全 IP,其中包括:

賽靈思的最新器件 (Versal? Premium ACAP)配備有硬化高速加密引擎 (HSC),可用作加密引擎,實現基于 AES-GCM 協議的高達 400Gb/s 的 MACSec、IPSec 或 SSL 處理。每個 HSC 引擎都能夠以 1x400G、2x200G 或 4x100G 通道化模式支持 MACSec、IPSec 和任何其他批量加密需求,每 100G 最多支持 128 個安全關聯 (SA)。采用可編程邏輯可以實現其他SA。

總結

由于通信網絡(邊緣、接入和核心網)正在向具有應用級政策感知功能的更高性能轉型,對更高吞吐量的安全處理的需求已經大幅增加。此外,隨著接入技術的升級以及 5G 接入技術 (xHaul)、新一代 PON 和有線網絡的部署,接入網絡的設備數量會以指數方式增長。新一代網絡安全設備需要具備 2~4 倍吞吐量,用于 L2 (MACSec) 安全與 L3 (IPSec) 安全處理。此外,新一代網絡會更多依賴意圖與策略,因此對高吞吐量應用級安全處理(L4-L7 安全)的需求已經顯著增加。高吞吐量應用安全實現方案需要高吞吐量數據包處理,以及用于加密需求的大量計算資源。純軟件應用安全實現方案無法滿足對性能與時延的期望。對于 5G 低時延應用來說,時延需求更加重要,因此,采用可編程加速器作為內聯安全處理器在新一代安全設備中的重要性日益突出。

在新一代防火墻中采用賽靈思器件不僅可以解決吞吐量和時延問題,其他優勢還包括助力新技術的實現,如:機器學習 (ML) 模型、安全訪問服務邊緣 (SASE) 和后量子加密 (PQC)。賽靈思器件可以為面向這些技術的硬件加速提供理想平臺,因為僅用軟件實現方案無法滿足性能需求。賽靈思正在針對現有的和新一代網絡安全解決方案不斷開發和升級IP、工具、軟件以及參考設計。