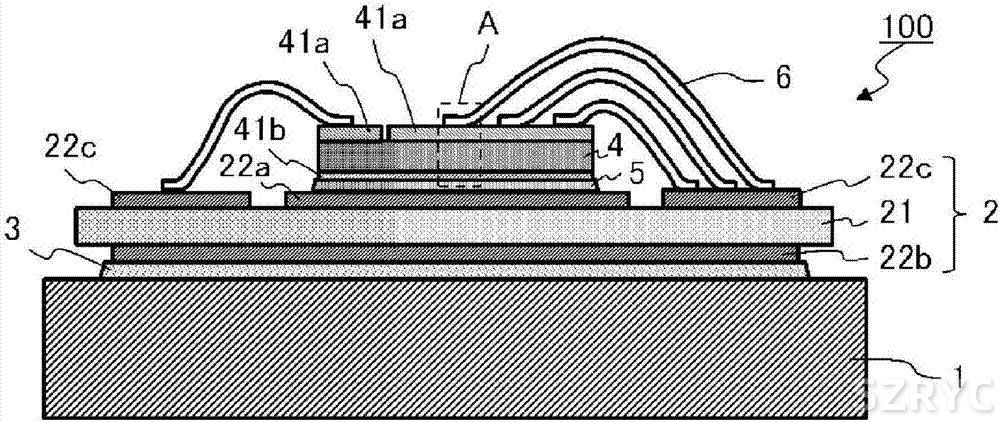

功率半導體的典型垂直封裝結構如圖所示。

在Si或SiC的器件表面上完成接線,并通過芯片貼裝向下釋放半導體中產生的熱量。目前,上表面的接線大多數是鋁引線鍵合(見圖),

近來已經替換為橫截面較大的條帶鍵合,但是在條帶鍵合工藝中減小壓力是一個問題。另外,現已開發了電阻率較低的銅引線,但是其鍵合工藝壓力比鋁鍵合高也是一個問題。人們想要的是能帶來低電阻的低壓力引線鍵合線工藝。氮化(GaN)具有橫向器件結構,但基本封裝結構與圖1.4相同。人們尤其希望硅上氮化具有成本競爭力,能很快形成市場。

模塊散熱是功率半導體中的一個技術問題。圖2中所示的單面散熱是用主流,但也有如圖3所示電裝公司的雙面冷卻類型。所有的貼裝都需要異的熱傳導結構。目前缺乏可以令人安全放心使用功率半導體的通用可靠性估技術和標準,無法評估性價比的優劣。此外,即使是Si功率半導體也經常現應用故障,對于功率密度更高的碳化硅和氮化,沒有經過考驗切實可行可靠性技術是無法使用的,因此迫切需要為產業發展設立標準。

在功率半導體的可靠性方面,需要考慮的因素很多,但是與故障最直相關的是在功率循環中產生的退化損傷。需要注意芯片貼裝部位的疲勞破壞陶瓷絕緣基板和結合界面的退化,或者引線鍵合界面的疲勞退化。尤其是芯片貼裝處的空洞阻礙器件工作期間的散熱,形成熱點,成為失效原因,所以必須在生產時盡量避免。此外,隨著工作溫度升高,電流密度顯著增加,因此必須充分注意電遷移對引線側的影響。電遷移已經成為硅器件中的鋁引線的主要問題,電遷移還會引起倒裝芯片的精細焊接失效。盡管也有引起芯片貼裝失效的情況,但是在芯片貼裝側還存在嚴重的應力載荷,使得

應力遷移和電遷移疊加作用。圖1中顯示的各個因素都是主要的器件性能退化機制。

寬禁帶功率半導體的預期工作結溫將超過200℃。這是當前硅封裝技術完全沒有涉及過的溫度范圍,并且模塊的每個部件都要承受嚴酷的溫度、應力和氧化/腐蝕性環境的考驗,必然會增加發生故障的可能性,因此必須調整組成材料和器件結構。下面列出的是封裝方面的要求:

1)可承受-50~300℃的嚴酷溫度循環的組成材料和結合結構;

2)在250~300℃空氣中抗氧化的界面設計;

3)闡明超高溫大電流下的電遷移退化機制以及相應的結構設計;

4)包括模塑樹脂的各種界面設計;

5)芯片貼裝缺陷、引線/條帶鍵合缺陷的檢測和可靠性評價。

另外,讀者應該注意到的是,當涉及模塊時,功率半導體的封裝技術還包括緩沖電容和電感的安裝配置。由于本書內容著重于連線和散熱,所以并未包含相關內容。