大約50年前,英特爾創造了世界上第一個商業生產的微處理器,一個普通的4位CPU(中央處理器),2300個晶體管,使用10μm工藝技術在硅中制造,只能進行簡單的算術計算。自這項突破性的成就以來,技術不斷發展,越來越復雜,目前最先進的64位硅微處理器已經擁有300億個晶體管(例如,AWS Graviton2微處理器,使用7納米工藝技術制造)。

微處理器現在已經深入到我們的文化中,已經成為一項元發明——也就是說,它是一種可以讓其他發明得以實現的工具,最近的一項發明使COVID-19疫苗在創紀錄的時間內開發所需的大數據分析成為可能。

本文報道了一種32位Arm架構的微處理器,采用金屬氧化物薄膜晶體管技術在柔性襯底(PlasticARM)上開發。與主流半導體行業不同,柔性電子產品通過超薄的外形、整合性、極低的成本和大規模生產的潛力,與日常用品無縫集成。PlasticARM是將數十億個低成本超薄微處理器嵌入日常用品的先驅。

與傳統半導體器件不同,柔性電子器件建立在諸如紙張、塑料或金屬箔等基底上,并使用有機或金屬氧化物或非晶硅等活性薄膜半導體材料。與晶體硅相比,它們有許多優點,包括薄、一致性和低制造成本。在柔性襯底上制備薄膜晶體管(TFTs)比在晶硅薄片上制備金屬-氧化物-半導體場效應晶體管(mosfet)的加工成本低得多。

TFT技術的目的不是要取代硅。隨著這兩種技術的不斷發展,硅很可能在性能、密度和功率效率方面保持優勢。然而,TFTs使電子產品具有新穎的外形因素和硅無法達到的成本點,從而極大地擴大了潛在應用的范圍。

微處理器是每一個電子設備的核心,包括智能手機、平板電腦、筆記本電腦、路由器、服務器、汽車,以及最近組成物聯網的智能物品。雖然傳統的芯片技術已經在地球上的每一個“智能”設備中嵌入了至少一個微處理器,但它面臨著讓日常物品更智能的關鍵挑戰,比如瓶子、食品包裝、服裝、可穿戴貼片、繃帶等等。成本是阻礙傳統硅技術在這些日常用品中可行的最重要因素。雖然芯片制造的規模經濟有助于大幅降低單位成本,但微處理器的單位成本仍然高得令人望而卻步。此外,硅芯片并不是天然的薄、柔韌性和一致性,而這些都是這些日常用品中嵌入電子產品的非常理想的特性。

另一方面,柔性電子產品確實提供了這些令人滿意的特性。在過去的20年里,柔性電子產品已經發展到提供成熟的低成本、薄的、柔性和兼容的設備,包括傳感器、存儲器、電池、發光二極管、能量采集器、近場通信/射頻識別和打印電路,如天線。這些是構建任何智能集成電子設備的基本電子元件。缺失的部分是柔性微處理器,目前還不存在可行的柔性微處理器的主要原因是,為了執行有意義的計算,需要將相對大量的TFT集成在柔性襯底上,這在以前的TFT技術中是不可能的。在這種技術中,在進行大規模集成之前需要一定程度的技術成熟度。

中間方法是將基于硅的微處理器芯片集成到柔性襯底上,也稱為混合集成,其中硅片變薄,芯片集成到柔性襯底上。雖然薄硅芯片集成提供了一個短期的解決方案,但該方法仍然依賴于傳統的高成本制造過程。因此,要在未來10年乃至更長的時間內生產數十億日常智能物品,這不是一個可行的長期解決方案。 我們的方法是利用柔性電子制造技術開發微處理器,也稱為柔性加工引擎。我們用柔性電子技術在聚酰亞胺基板上構建本機柔性微處理器。金屬氧化物薄膜晶體管成本低,而且可以縮小到大規模集成所需的較小幾何尺寸。 早期的原生靈活處理器工作是基于使用低溫多晶硅TFT技術開發8位CPU,這具有較高的制造成本和較差的橫向可伸縮性。最近,二維材料晶體管被用于開發處理器,如使用二硫化鉬(MoS 2)晶體管的1位CPU 13和使用互補碳納米管晶體管構建的16位RISC-V CPU。然而,這兩項工作都是在傳統的硅片而不是柔性襯底上進行的。

第一次嘗試構建基于金屬氧化物TFT的處理元件是一個8位算術邏輯單元,它是CPU的一部分,與在聚酰亞胺上制造的打印可編程ROM相結合。最近,Ozer等人在金屬氧化物TFTs中提出了天生靈活的專用機器學習硬件。盡管機器學習硬件擁有最復雜的柔性集成電路(FlexIC),它由1400個門的金屬氧化物TFT組成,但FlexIC不是一個微處理器。可編程處理器方法比機器學習硬件更通用,并支持豐富的指令集,可用于對從控制代碼到數據密集型應用程序(包括機器學習算法)的各種應用程序進行編程。

原生柔性微處理器有三個主要部件:(1)32位CPU,(2)包含CPU和CPU外設的32位處理器,(3)包含處理器、存儲器和總線接口的片上系統(SoC),所有這些部件都是用金屬氧化物TFT在柔性基板上制造的。本機靈活的32位處理器源自支持Armv6-M架構的Arm Cortex-M0+處理器(一組80多條指令)和現有的軟件開發工具鏈(例如,編譯器、調試器、連接器、集成開發環境等)。整個靈活的SoC被稱為PlasticARM,能夠從其內部內存運行程序。PlasticARM包含18334個NAND2等效柵極,這使其成為迄今為止在柔性基片上使用金屬氧化物tft制造的最復雜的FlexIC(至少比以前的集成電路復雜12倍)。

PlasticARM系統架構

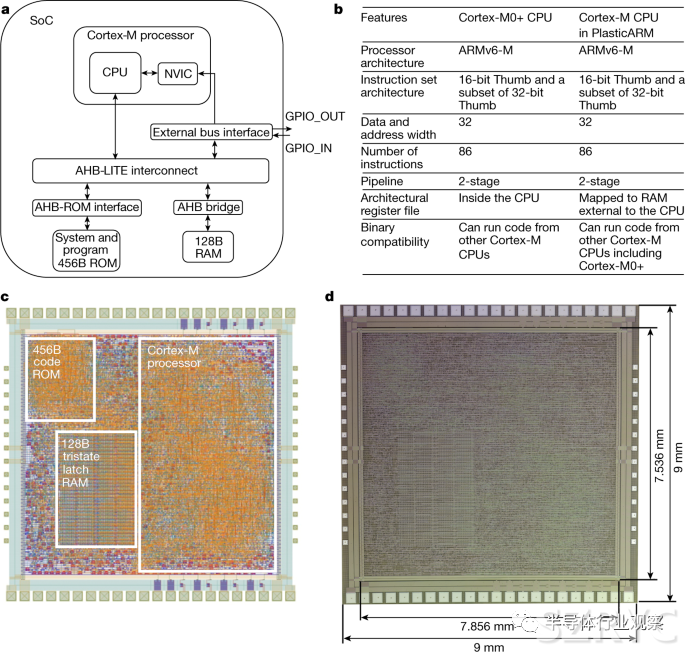

PlasticARM的芯片架構如下圖所示。它是一種SoC,包括源自32位Arm Cortex-M0+處理器產品的32位處理器、存儲器、系統互連結構和接口塊以及外部總線接口。

PlasticARM架構和特性

a,SoC架構,顯示了內部結構、處理器和系統外設。處理器包含一個32位的Arm Cortex-M CPU和一個嵌套向量中斷控制器(NVIC),并通過互連結構(AHB-LITE)連接到它的內存。最后,外部總線接口提供了通用輸入輸出(GPIO)接口,用于芯片外與測試框架通信。

b,與Arm Cortex-M0+CPU相比,PlasticARM使用的CPU的特點。這兩個cpu都完全支持Armv6-M架構,32位地址和數據能力,以及來自整個16位Thumb和32位Thumb指令集架構的一個子集的86條指令。CPU微架構具有兩級流水線。寄存器在Cortex-M0+的CPU中,但在PlasticARM中,寄存器被移動到SoC中的基于鎖存的RAM中,以節省Cortex-M的CPU區域。最后,兩個CPU之間以及與同一體系結構家族中的其他CPU之間都是二進制兼容的。

c,PlasticARM的模具布局,,表示Cortex-M處理器、ROM和RAM等白框中的關鍵塊。

d,PlasticARM的模具顯微圖,顯示模具和核心區域的尺寸。

該處理器完全支持Armv6-M指令集架構,這意味著為Cortex-M0+處理器生成的代碼也將在其派生的處理器上運行。處理器包括CPU和一個與CPU緊密耦合的嵌套向量中斷控制器(NVIC),處理來自外部設備的中斷。 SoC的其余部分包括存儲器(ROM/RAM)、AHB-LITE互連結構(高級高性能總線(AHB)規范的一個子集)和將存儲器連接到處理器的接口邏輯,以及用于控制兩個通用輸入輸出(GPIO)引腳進行片外通信的外部總線接口。ROM包含456字節的系統代碼和測試程序,并已實現為組合邏輯。128字節的RAM已經實現為一個基于鎖存的寄存器文件,主要用作堆棧。

上圖b顯示了PlasticARM中使用的Cortex-M與Arm Cortex-M0+的比較。雖然PlasticARM中的Cortex-M處理器不是一個標準產品,但它實現了支持16位Thumb和32位Thumb指令集架構的一個子集的Armv6-M架構,因此它與同一架構家族中的所有Cortex-M類處理器(包括Cortex-M0+)都是二進制兼容的。

PlasticARM中的Cortex-M和Cortex-M0+之間的關鍵區別在于,我們將SoC中RAM的特定部分分配給CPU寄存器(約64字節),并將它們從CPU移動到PlasticARM中Cortex-M中的RAM,而Cortex-M0+中的寄存器仍保留在其CPU中。通過消除CPU中的寄存器,并使用現有RAM作為寄存器空間,以較慢的寄存器訪問為代價,實現了CPU面積的大幅縮減(約3倍)。

結果

PlasticARM采用PragmatIC的0.8μm工藝,采用工業標準芯片實現工具。為了實現PlasticARM FlexIC,我們開發了工藝設計工具包、標準單元庫和器件/電路模擬。上圖c顯示了FlexIC布局,其中劃分了Cortex-M處理器、RAM和ROM。實現方法的細節可以在Methods中找到。 PlasticARM是使用商業的“fab-in-a-box”生產線FlexLogIC制作的,其芯片顯微照片如上圖d所示。該工藝使用基于IGZO的n型金屬氧化物TFT技術,并在直徑為200 mm的聚酰亞胺晶圓上生成FlexIC設計。IGZO TFT電路是使用傳統的半導體加工設備制成的,該設備適用于在厚度小于30μm的柔性(聚酰亞胺)襯底上生產器件。其通道長度為0.8μm,最小供電電壓為3v。

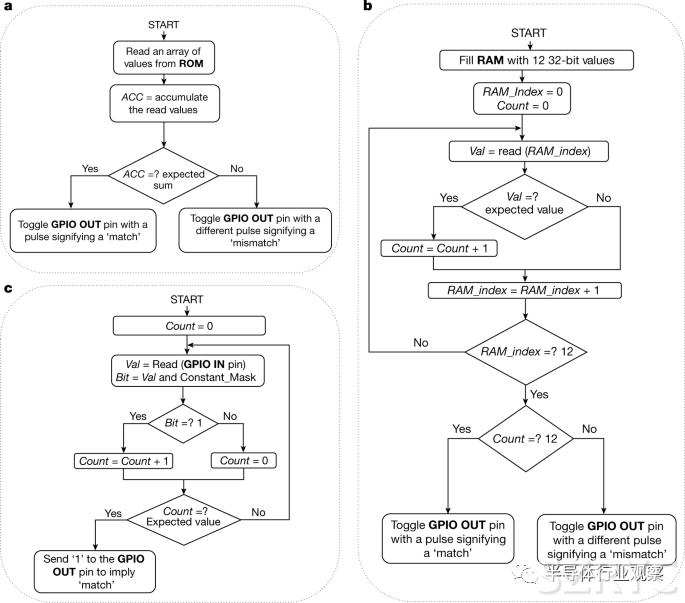

n型金屬氧化物薄膜技術的設計面臨著許多相同的挑戰,這些挑戰影響了20世紀70年代和80年代初第一代硅(負溝道金屬氧化物半導體,NMOS)技術的復雜性和產量,特別是低噪聲容限、高功耗和大的工藝變化。制造方法的細節可以在“方法”中找到。 我們報道了一種功能齊全的彈性塑料臂這已經通過在制造之前運行預編程(硬連線)到ROM中的三個測試程序來證明。盡管測試程序是從ROM執行的,但這不是系統的要求;它簡化了PlasticARM的測試設置。當前的ROM實現不允許在制造之后改變或更新程序代碼,盡管這在將來的實現中是可能的(例如,通過可編程ROM)。 測試程序的編寫方式使得指令執行CPU內部的所有功能單元,如算術邏輯單元、加載/存儲單元和分支單元,并使用設置為“cortex-m0plus”的CPU標志,使用armcc編譯器進行編譯。測試程序的流程圖和詳細描述如圖2所示。當每個測試程序完成其執行時,測試程序的結果通過輸出GPIO pin-off芯片傳輸到測試框架。

測試程序

a,一個簡單的累加程序從ROM中讀取值并將它們相加。如果總和與預期值匹配,則會向測試儀讀取的GPIO輸出引腳發送確認信號。該測試使用加載、添加、比較和分支指令。

b,一組32位整數值被即時寫入RAM并在檢查讀取值與預期值的同時將它們讀回。如果所有寫入的值都被正確讀取,則會向GPIO輸出引腳發送確認信號。該測試使用加載、存儲、添加、移位、邏輯、比較和分支指令。

c,從測試儀通過GPIO輸入引腳連續讀取一個值。該值被一個常量值屏蔽。如果屏蔽結果為1,則計數器遞增。如果為0,則計數器復位。如果計數器值等于預期值,則會向GPIO輸出引腳發送確認信號。該測試使用加載、存儲、添加、邏輯、比較和分支指令。斜體字表示測試程序中的變量;粗體和大寫的術語是引腳和存儲。

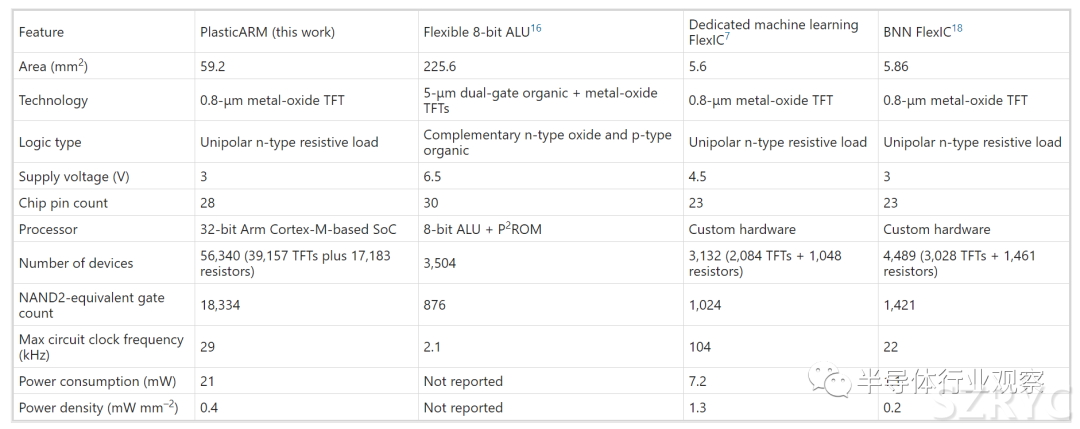

眾所周知,IGZO TFT可以彎曲到3毫米的曲率半徑而不會損壞,PragmatIC還通過將其自己的電路反復彎曲到這個曲率半徑來驗證這一點。然而,所有PlasticARM測量都是在柔性晶圓保留在其玻璃載體上的情況下進行的,使用位于Arm Ltd的標準晶圓測試設備,在室溫下進行。PlasticARM的測量結果與其模擬結果進行了驗證。測量設置、結果及其對模擬的驗證的詳細信息可以在方法中找到。 表1顯示了PlasticARM的實現和測量的電路特性,并與以前使用金屬氧化物TFTs構建的最佳天然柔性集成電路進行了比較。PlasticARM的面積為59.2 mm 2(無焊盤),并包含56340個器件(n型TFT加電阻)或18334個NAND2等效門,至少比之前最好的集成電路(即二進制神經網絡(BNN)FlexIC)高出12倍。微處理器的時鐘頻率最高可達29 kHz,功耗僅為21 mW,主要是(>99%)靜態功耗,其中處理器占45%,存儲器占33%,外設占22%。SoC使用28個引腳,包括時鐘、復位、GPIO、電源和其他調試引腳。此設計中沒有使用專門的靜電放電緩解技術。相反,所有輸入都包含140pF電容器,而所有輸出都由帶有有源上拉晶體管的輸出驅動器驅動。

表1:用金屬氧化物TFT構建的柔性集成電路的優點 任何電阻負載技術的一個關鍵挑戰是功耗。我們預計正在開發的低功耗單元庫將支持更高的復雜性,高達約100000個門。遷移到超過1000000個門可能需要互補金屬氧化物半導體(CMOS)技術。

結論

我們報道了一種柔性32位微處理器PlasticARM,采用0.8μm金屬氧化物TFT技術制作。我們已經演示了一個SoC的功能,它有一個32位Arm處理器制作在一個靈活的襯底上。它可以利用現有的軟件/工具支持(比如編譯器),因為它與Armv6-M架構中的Arm Cortex-M類處理器兼容,所以不需要開發軟件工具鏈。最后,據我們所知,它是目前為止用金屬氧化物tft制作的最復雜的柔性集成電路,包含超過18000個柵極,至少比以前最好的集成電路高12倍。 我們設想,PlasticARM將率先開發低成本、完全靈活的智能集成系統,使“萬物互聯”成為可能,包括在未來10年將超過一萬億無生命物體集成到數字世界中。為日常用品提供超薄、兼容、低成本、天生靈活的微處理器將帶來創新,從而帶來各種研究和商業機會。

方法

執行

為了充分利用現代集成電路設計流程提供的高度自動化、快速周轉實現和驗證,我們開發了一個小型標準單元庫。標準單元庫是一些小的預先驗證構建塊的集合,使用復雜的電子設計自動化工具,如合成、放置和布線,可以快速而輕松地構建更大更復雜的設計。 在開始實施標準單元庫之前,先進行了一些初步調查,以便在目標技術的限制下確定最適合該庫的標準單元架構。單元架構是庫中每個單元共有的一組特征,例如單元高度、電源帶尺寸、布線網格等,它們允許單元以標準方式咬合在一起以形成更大的結構。這些共同特征主要受制造過程的設計規則支配,但也受最終設計的性能和面積要求的影響。

一旦建立了單元架構,下一步就是確定單元庫的內容,不僅要考慮各種邏輯功能,還要確定每個邏輯功能的驅動強度變體的數量。由于設計、實施和表征每個標準單元所涉及的工作量很大,因此決定使用小型原型庫進行一些試驗,然后根據需要擴展庫。為了評估這個小型原型標準單元庫的性能,實施、制造和測試了一些簡單的代表性電路(例如環形振蕩器、計數器和移位陣列)。 我們從1.0-μm設計規則遷移到新的FlexIC 0.8-μm設計規則以減少面積,從而提高產量。由于這意味著用更小的晶體管重新繪制庫中的每個單元,我們也借此機會更改了標準單元架構,以包括MT1(金屬跟蹤1)引腳,以便路由器更容易連接單元。電阻材料的改進(更高的薄層電阻,R s)也使電阻器的尺寸減小了3倍。 晶體管和電阻器尺寸的顯著減小使大多數單元的面積減少了約50%(參見擴展數據圖1),這反過來又通過降低設計的整體尺寸提高了制造良率。但是,由于仍然存在制造良率問題,我們可以通過更改標準單元架構來進一步緩解這些問題,因此再次重新繪制了該庫。這一次,我們專注于可以提高最終設計整體良率的事情,例如包含冗余過孔和觸點、減少源極-漏極多邊形中的頂點數量(如果可能)以及將堆疊晶體管的尺寸保持在最低限度。此外,我們恢復到較低的薄層電阻以改善工藝擴展,但我們能夠通過使用更窄的電阻器來保持面積節省。為了提高邏輯綜合的整體質量,庫中添加了許多復雜的AND-OR-INVERT和OR-AND-INVERT邏輯門以及一些高驅動強度的簡單邏輯門,例如NAND2_X2和NOR2_X2。

FlexLogIC工藝是NMOS工藝,因此依賴電阻負載將單元輸出拉向電源以驅動邏輯1。因此,單元輸出上升時間比下降時間慢得多,而且這種不對稱性會影響性能,尤其是對于重載網絡。為了改善關鍵網絡(例如時鐘)的時序,我們添加了帶有有源晶體管上拉的緩沖器。雖然這些有源上拉增加了少量的面積,但它們確實具有降低靜態功耗的額外好處。具有上拉電阻和有源晶體管上拉的緩沖器的布局和模擬傳輸特性如圖2所示。 這個簡單的標準單元庫隨后被成功用作目標技術,使用基于行業標準電子設計自動化工具的典型集成電路設計流程來實現PlasticARM SoC。擴展數據表1顯示了標準單元庫內容和單元使用信息。 由于我們還沒有專用的靜態隨機存取存儲器FlexIC,我們通過將一些修改過的標準單元小心地放置在一個平鋪的陣列中,通過鄰接連接形成一個32×32位的存儲器(這個塊可以在圖1c中的芯片布局)。 FlexLogIC技術(見擴展數據表2)有四個可路由的金屬層,其中只有較低的兩層在標準單元內使用。這使得最上面的兩層金屬層可以用于標準電池之間的互連,然后可以在相鄰電池的頂部進行路由,從而大大提高了總體柵極密度,約為每平方毫米300個柵極。

制造

擴展數據表2中總結了工藝參數和TFT參數的統計變化.FlexLogIC是一種專有的200毫米晶圓半導體制造工藝,可創建金屬氧化物薄膜晶體管和電阻器的圖案層,根據FlexIC設計將四個可布線(無金)金屬層沉積在柔性聚酰亞胺基板上。FlexIC設計的重復實例是通過運行多個薄膜材料沉積、圖案化和蝕刻序列來實現的。為了便于操作并允許使用行業標準工藝工具并實現亞微米圖案化特征(低至0.8μm),柔性聚酰亞胺基板在生產開始時旋涂到玻璃上。該工藝已經過優化,以確保在20毫米的橫向距離內厚度變化基本上小于3%。薄膜材料沉積是通過物理氣相沉積、原子層沉積和溶液處理(例如旋涂)的組合實現的。基板處理條件已經過精心優化,以最大限度地減少薄膜應力和基板彎曲。使用光刻5倍步進器工具實現特征圖案化,該工具對在200毫米直徑晶圓上的多個實例重復的鏡頭進行成像。

每個鏡頭都是單獨聚焦的,這進一步補償了旋鑄薄膜內的任何厚度變化。技術測量是使用過程控制監控結構進行的。使用光刻5倍步進器工具實現特征圖案化,該工具對在200毫米直徑晶圓上的多個實例重復的鏡頭進行成像。每個鏡頭都是單獨聚焦的,這進一步補償了旋鑄薄膜內的任何厚度變化。技術測量是使用過程控制監控結構進行的。使用光刻5倍步進器工具實現特征圖案化,該工具對在200毫米直徑晶圓上的多個實例重復的鏡頭進行成像。每個鏡頭都是單獨聚焦的,這進一步補償了旋鑄薄膜內的任何厚度變化。技術測量是使用過程控制監控結構進行的。

模擬、測試和驗證

我們使用測試測量設置捕獲了功能性PlasticARM FlexIC的時序特性,并將測量結果與其寄存器傳輸級(RTL)仿真的結果進行比較,以驗證功能。 RTL仿真如圖3所示。它首先將RESET輸入設置為“0”,將PlasticARM重置為已知狀態。然后RESET設為'1',處理器從重置狀態釋放,開始從ROM執行代碼。首先,GPIO[0]輸出引腳被切換一次,然后執行如圖2所示的三個測試。在第一個測試中,從ROM中讀取數據并將其添加到累加器中,并與期望值進行比較(見圖2a)。

如果值匹配,將兩個脈沖的短脈沖發送到GPIO[0],如圖3a擴展數據所示。如果值不同,擴展數據圖3b中GPIO[0]上脈沖的周期和占空比會增加。在第二個測試中(圖2b),將數據寫入RAM,讀回并進行比較。如果數據在從RAM中寫入或讀取時沒有損壞,則3個脈沖的短脈沖發送到GPIO[0],如圖3a中的擴展數據所示。如果數據被破壞,GPIO[0]上脈沖的周期和占空比會像以前一樣增加。在最后的測試中(圖2c),處理器進入一個無限循環并測量GPIO輸入引腳[1]上應用'1'的時間。如果GPIO[1]保持在'1'而沒有任何故障,GPIO[0]從'0'變為'1'。PlasticARM的時鐘頻率為20khz。由于它不使用任何計時器,軟件中選擇了一個值來表示GPIO[1]信號在20khz工作時保持在'1'約1秒。在擴展數據圖3a的模擬中,該值對應于20,459個時鐘周期,在20 kHz時產生1.02295 s。 制造完成后,PlasticARM在晶圓探針臺上進行測試,同時仍連接到玻璃載體上。

數據可用性 在測試和驗證中生成波形的數據可根據要求從相應的作者處獲得。 代碼可用性 三個驗證PlasticARM的測試程序的代碼可向相應作者索取。