高效互連使復(fù)雜的SoC交付變得更容易,更可預(yù)測和更低成本。

片上系統(tǒng)(soc)正日益成為一種網(wǎng)絡(luò),您可以在其中添加單獨的知識產(chǎn)權(quán)(IP)模塊。SoC IP模塊包括處理器、內(nèi)存控制器、專用子系統(tǒng)和 I/O——這些模塊可以從互連IP中分離開來,并放入日益復(fù)雜的SoC分區(qū)。在不久的將來,當(dāng)允許電子系統(tǒng)進行決策時,需要越來越復(fù)雜的SoC。

互連要處理SoC內(nèi)部各種各樣的通信,是一種高效的IP模塊集成機制。互連是SOC內(nèi)部可配置性最高的IP——通常在一個項目期間會多次更改,而且?guī)缀蹩偸窃诓煌椖恐g變動。它在信息安全性和功能安全性方面也扮演著重要的角色,因為它承載了SoC的大部分?jǐn)?shù)據(jù),并且包含幾乎所有SoC內(nèi)部長連線和系統(tǒng)級服務(wù),包括服務(wù)質(zhì)量(QoS)、可見性、物理感知和電源管理。互連能夠?qū)崿F(xiàn)多處理器SoC緩存一致性,提升高級駕駛輔助系統(tǒng)(ADAS)汽車芯片和網(wǎng)絡(luò)SOC的性能與帶寬級別,而且能夠在長時間運行的消費類設(shè)備中實現(xiàn)超低功耗。

互聯(lián)IP必須不斷發(fā)展,以推動創(chuàng)新SoC應(yīng)用于新興行業(yè),如正在興起的人工智能(AI)和機器學(xué)習(xí)(ML) 應(yīng)用,這類應(yīng)用正推動數(shù)據(jù)中心自動化和自動駕駛方面的創(chuàng)新。

隨著工藝尺寸不斷縮小,soc互連變得更加關(guān)鍵。將芯片劃分為可復(fù)用IP的功能電路模塊,或稱為“芯粒(chiplet)”,不僅可以提高裸片的良品率,而且能在現(xiàn)今的16納米及以下工藝中增加更多功能。借助Chiplet集成方法,開發(fā)人員能夠?qū)⒍嗉夜鹃_發(fā)的裸片或具有特定功能(如內(nèi)存和I/O)的芯片集成在單一封裝中。

互連的大小通常約為整個SoC的10%,但它會顯著影響SoC的質(zhì)量、性能和交付進度。與SoC總體預(yù)算相比,互連IP的初始許可成本相對較小,但是“低效”互連可能會導(dǎo)致進程、成本和規(guī)范問題。例如,如果互連不能在設(shè)定的目標(biāo)性能關(guān)閉時序,SoC將無法滿足頻率規(guī)范,這可能導(dǎo)致設(shè)計失敗。

應(yīng)用于多個SoC項目的高性能互連IP需要滿足多種標(biāo)準(zhǔn),包括:

架構(gòu)的靈活性-- 互連必須適應(yīng)各種拓撲架構(gòu),以實現(xiàn)必要的靈活性。例如,互連架構(gòu)必須具備樹狀結(jié)構(gòu)(最適合于異構(gòu)SoC)以及常規(guī)拓撲,包括網(wǎng)格、環(huán)狀和圓形(AI和網(wǎng)絡(luò)SoC所需要)。互連IP也必須能夠“向下擴展”以滿足IP子系統(tǒng)和SoC服務(wù)互連等項目的低端互連需求。

例如,僅具有角路由器交換的互連可能適用于高端網(wǎng)絡(luò),但不適用于移動SoC,在移動SoC中,功耗、面積和延遲最小化是非常重要的。另一方面,缺乏角落路由器交換不利于交付高端服務(wù)器設(shè)計或人工智能/機器學(xué)習(xí)加速器 。同樣,能夠處理非相關(guān)性通信但不支持緩存一致性的互連就會限制緩存一致性SoC架構(gòu)的選擇。協(xié)議轉(zhuǎn)換功能是指互連可以支持各種IP模塊通信協(xié)議,可以最大化設(shè)計中所選用的IP模塊。

性能——性能表現(xiàn)可分為三大類:

●頻率——如果互連不能達到目標(biāo)頻率,就會限制SoC的性能。例如,如果處理器以4 GHz運行,而高速緩存一致性互連不能以2 GHz運行,則性能將受到限制。然而,并非SoC中的所有路徑都是相同的。擁有多種頻率域和速率自適應(yīng)能力是至關(guān)重要的,這樣各個路徑可以在不同的頻率下運行。畢竟,當(dāng)只有一些路徑需要以指定的最高頻率運行時,為什么要為整個互連支付高性能路徑的費用?

●延遲——延遲由數(shù)據(jù)包從啟動程序到目標(biāo)IP模塊所需的周期數(shù)決定。它依賴于互連IP的效率、到達目的地的線路長度以及互連IP功能的物理位置。互連物理感知在16nm及以下的制程工藝中至關(guān)重要,因為必須在RTL(寄存器傳輸級別)階段盡早估計時序收斂,以避免在布局布線階段中出現(xiàn)問題。

延遲和頻率之間需要作一個權(quán)衡: 如果頻率高,則需要更多管道,這會增加延遲。對于延遲敏感的處理器到內(nèi)存路徑,最小化延遲尤其重要。好消息是SoC中對延遲有苛刻要求的路徑相對較少,但是請記住,這些路徑上的額外延遲周期通常會成為系統(tǒng)級SoC性能的約束。路徑越長,用于生成路徑的線路越多,則必須添加更多管道來滿足時序限制。片上網(wǎng)絡(luò)(NoC)互連采用分布式交換,通常比采用集中交叉的混合總線模式具有更低的延遲。分布式仲裁進一步縮短了交換單元之間的路徑。并非所有網(wǎng)絡(luò)都具有延遲臨界性,所以互連應(yīng)該為高延遲路徑提供靈活性,例如,僅在SoC的初始操作期間使用的I/O IP模塊。在SoC設(shè)計中,具有高延遲的路徑能力可以節(jié)省連線。

●帶寬/吞吐量——帶寬是給定路徑上數(shù)據(jù)傳輸?shù)淖畲笏俾省M掏铝渴侵笖?shù)據(jù)沿著互連路徑成功傳輸?shù)牧俊M掏铝靠赡苁艿交ミB體系結(jié)構(gòu)、實現(xiàn)拓撲和數(shù)據(jù)包協(xié)議的限制。有效互連能夠讓性能盡可能接近理論帶寬的性能;低效互連會造成瓶頸。一種能夠支持8位低帶寬連接到1024位高帶寬的互連——以及兩者之間的互連寬度——為設(shè)計人員提供最大靈活性的架構(gòu)。

面積——硅在任何SoC設(shè)計中都是一個成本因素。一個有用的度量標(biāo)準(zhǔn)是,按照16nm制程標(biāo)準(zhǔn),每顆SoC 中1平方毫米硅的成本通常為10美分。使用更少的電線和柵極以及更高效的互連拓撲可以節(jié)約成本。如果面積能減少超過5平方毫米,產(chǎn)量將提高,并能節(jié)約額外成本。由于面積效率高的互連通常占SoC面積的10%左右,因此,互連面積縮減30-50%,芯片級SOC就能少用幾平方毫米的硅。粗略地算,一個面積效率高的互連將在一個100平方毫米的SoC上節(jié)省大約3-5平方毫米,那么每顆SoC將節(jié)省30-50美分,這具體取決于生產(chǎn)效率。

功率——-在獨立的消費類或物聯(lián)網(wǎng)(IoT)設(shè)備中,功耗是必不可少的。在主動電源模式下,互連IP比CPU和GPU消耗更少的電量,但當(dāng)任務(wù)完成時,這些可以快速關(guān)閉。事實上,對于大多數(shù)電池供電的系統(tǒng)來說,待機耗電量是電池壽命的決定因素。在沒有數(shù)據(jù)通信但時鐘處于打開狀態(tài)時,妥善管理互連功耗對空閑狀態(tài)的功耗(或待機功耗)至關(guān)重要。

對于大部分時間處于空閑模式的電池供電系統(tǒng),需要一個低功耗的互連。這個互連IP必須通過三級時鐘門來實現(xiàn)功率控制策略,以便輕松創(chuàng)建多個電源域,在一個周期內(nèi)啟動一個電源域,并實現(xiàn)低功率域交叉。對于16nm的互連功耗來說,一個合理的度量標(biāo)準(zhǔn)是每百萬個互連邏輯門的空閑功耗小于0.5mW。

功能安全性——關(guān)鍵性的應(yīng)用必須符合嚴(yán)格的安全標(biāo)準(zhǔn),如汽車市場上的ISO 26262標(biāo)準(zhǔn)。為滿足ISO26262中ASIL(汽車安全完整性等級)B、C和D的要求,互連IP實現(xiàn)要求具有彈性功能,以補償系統(tǒng)級和隨機性錯誤,達到所需的故障檢測和保護等級。為了滿足最高級別的ASIL D ,互連IP需要網(wǎng)絡(luò)接口單元邏輯復(fù)制、ECC(糾錯碼)和/或奇偶校驗位數(shù)據(jù)路徑保護以及數(shù)據(jù)包完整性檢查。互連IP供應(yīng)商還必須能夠提供功能安全手冊,以及相應(yīng)的分析和操作資料,以證明互連IP適合在符合ISO26262標(biāo)準(zhǔn)的系統(tǒng)中使用。沒有這樣的文件和操作資料,就很難在最終的電子系統(tǒng)中鑒定半導(dǎo)體元器件。

信息安全性——功能安全可靠性可以保護soc免受制造和環(huán)境錯誤的影響,而信息安全性可以保護關(guān)鍵性芯片免受人為攻擊。有效的互連必須能夠?qū)崿F(xiàn)防火墻,該防火墻通常由設(shè)計團隊配置的。當(dāng)數(shù)據(jù)從SoC的某一區(qū)域傳輸?shù)搅硪粎^(qū)域時,必須提供區(qū)域隔離功能,以實現(xiàn)安全性。這些互連硬件特性應(yīng)與整個系統(tǒng)級安全方案無縫集成并增強其安全性。

生產(chǎn)效率——高效的互連工具可加速部署,并提升SoC設(shè)計進程的可預(yù)測性。互聯(lián)IP軟件工具應(yīng)包括:

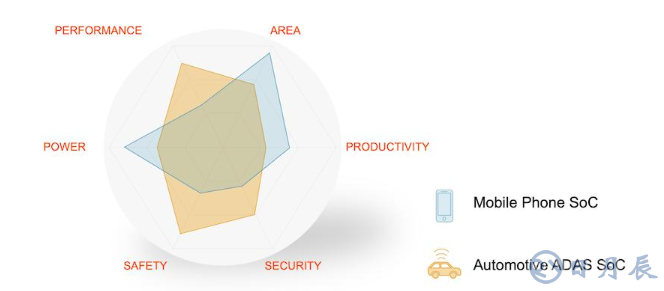

圖1。片上互連必須滿足各類芯片的不同要求。(來源:Arteris IP)

IP和電子設(shè)計自動化(EDA)產(chǎn)品的生態(tài)系統(tǒng)意味著支持ARM、Synopsys和Cadence等公司的多種IP協(xié)議。它還意味著與領(lǐng)先和初創(chuàng)EDA供應(yīng)商的仿真、模擬、驗證、功能安全、建模以及布局繞線工具的集成。世界級的互連生產(chǎn)效率軟件以及與其它IP和EDA工具的集成可以降低SoC項目的研發(fā)成本和進度時間。

IP成本計算

雖然互連IP只占SoC面積的10%,但它可能導(dǎo)致延遲,甚至錯過系統(tǒng)設(shè)計窗口。最好的情況便是,次優(yōu)級SoC可能會導(dǎo)致時序問題、引發(fā)阻止SoC運行的死鎖、造成SoC子系統(tǒng)的數(shù)據(jù)匱乏、帶寬瓶頸,以及功能缺失,這會增加不可預(yù)見解決方案的研發(fā)費用和延遲。因此,高性能和經(jīng)過驗證的互連對SoC設(shè)計項目的成功起著至關(guān)重要的作用。

結(jié)論

高效互聯(lián)IP開發(fā)需要多年的努力,可能需要花費7千萬至1億美金。走捷徑會導(dǎo)致失望,并花費大量業(yè)務(wù)成本。為單個芯片設(shè)計互連是一個挑戰(zhàn),但提供一個適用于多個SoC設(shè)計的廣泛互連解決方案需要資金、規(guī)模和承諾。組建并留住IP團隊可能會遇到挑戰(zhàn),他們必須是跨學(xué)科人才(架構(gòu)師、硬件工程師、軟件開發(fā)人員和驗證工程師),并在開發(fā)項目期間保持多年的合作。

有效的互連使交付復(fù)雜的SoC變得更容易、更可預(yù)測,同時降低設(shè)計成本。SoC項目總監(jiān)只需要選擇合適的互連。