引 言

在較長的一段時間內,脈沖重復頻率跟蹤器技術都是基于ISA總線且建立在分立式IC器件架構之上,存在著元器件數量偏多、PCB(印制電路板)尺寸偏大、總線分時復用速度慢、電路穩定性不夠理想、擴展性與移植性差等缺陷。當前,FPGA(現場可編程門陣列)器件技術已經發展得非常成熟,如何將其很好地應用在重復頻率跟蹤器技術之中,將數字式重復頻率跟蹤器技術模塊化,減少跟蹤器的元器件使用數量,縮小外形尺寸,提高跟蹤器的穩定性與擴展性,加強跟蹤器的可移植性,成為我們研究的一個目標。

比較以往的分立式重復頻率跟蹤器,模塊化的數字式重復頻率跟蹤器的主要優點為:高集成度、高可靠性,體積小、速度快,配置靈活、生命周期長,良好的可擴展性和可移植性,風險小、性價比高、研制周期短。

1 、組成與工作原理

1.1 組成

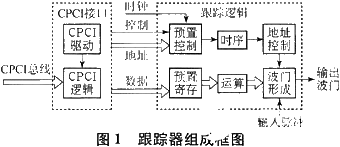

模塊化的數字式重復頻率跟蹤器組成框圖如圖1所示。

該跟蹤器由CPCI接口電路和跟蹤邏輯電路兩大部分組成。其中,CPCI接口電路包括CPCI驅動單元和CPCI邏輯單元兩個功能模塊,跟蹤邏輯電路包括預置控制單元、預置寄存單元、時序單元、運算單元、地址控制單元和波門形成單元共6個功能模塊。

1.2 工作原理

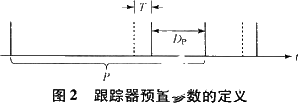

模塊化的數字式重復頻率跟蹤器的主要功能是從一脈沖流中分離出某一固定重復頻率的脈沖序列(及實施對某一固定重復頻率的跟蹤),主要包括3個預置參數:P、DP和T,其中,P為信號重復周期(在跟蹤器的實際應用中,雖然以重復周期為參數,但業內仍習慣稱為重復頻率跟蹤器),DP為容差(跟蹤輸出信號寬度控制參數),T為提前量(跟蹤輸出信號與輸入信號相關后的脈沖沿控制參數)。重復頻率跟蹤器就是根據這3個預置參數對輸入脈沖信號進行實時跟蹤,形成所需的輸出波門信號,且P、DP和T值均由計算機通過CPCI總線預置,這3個預置參數的定義見圖2。

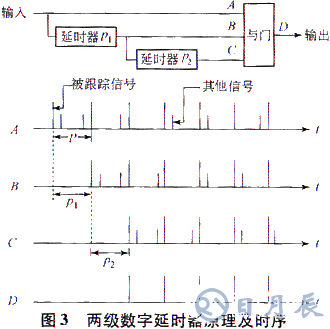

在跟蹤器中,有一個關鍵電路是數字延時器,其基本原理是對輸入脈沖流的到達時間進行處理。對于一個重復頻率相對穩定的脈沖信號,在延遲一個信號重復周期后,與信號本身自相關。根據這一原理,如果延遲時間等于脈沖信號的重復周期(即P=1/F,F為原始脈沖信號重復頻率),那么讓原始信號通過延時器后再與原始信號相“與”,將會得到一個信號重復頻率與原始信號相同的有效輸出信號。在實際應用中,為了從交錯脈沖流中可靠分離出被跟蹤信號,有效去除其他干擾信號,一般采用具有兩級數字延時器的延遲電路,其原理及時序見圖3。其中,P=1/F(F是被跟蹤信號重復頻率),如果滿足p1=p2=P(p1、p2分別對應兩級延時器的延遲時間),該電路就能夠從交迭脈沖流中分離出一固定重復頻率的脈沖序列。

上述數字延時器的核心器件為存儲器,其工作特性為輸入信號從存儲器輸入端Data寫入,經過設定大小的讀寫周期后,從輸出端Q讀出,如果讀地址與寫地址的差值為P,那么從輸入端到輸出端原始信號被延時了P個讀寫周期。在實際應用中,考慮到信號的抖動和對輸出脈沖寬度及時間沿的不同需求,將容差參數DP和提前量參數T引入延時周期,將延時周期設計為P-DP-T,并對輸出脈沖后沿作延時一個DP的處理,這樣,得到的最終輸出波門信號寬度與參數DP相關,時間沿與參數T相關,達到了輸出波門信號參數可控的目的。

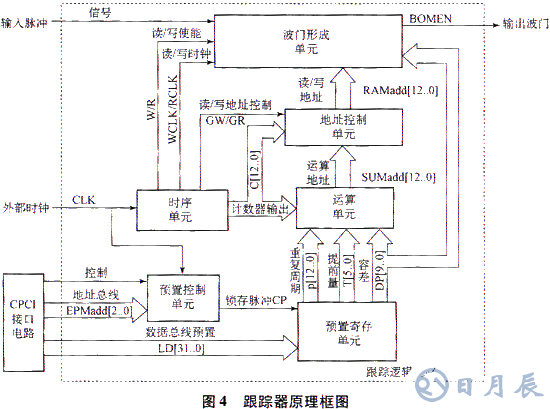

整個跟蹤器電路的原理框圖見圖4。

跟蹤器的3個預置參數通過數據總線預置后進入預置寄存單元鎖存,地址線和控制線進入預置控制單元通過組合邏輯生成預置寄存單元的鎖存脈沖CP;外部時鐘進入時序單元后通過組合邏輯生成讀/寫地址控制信號、讀/寫使能信號、瀆/寫時鐘、計數器輸出,其中,讀寫時鐘和計數器輸出與外部時鐘周期相關,整個跟蹤器的跟蹤精度也就與外部時鐘相關,例如,當外部時鐘為1 MHz時,計數器輸出以1μs為一個計數節拍。在實際應用中,需要綜合考慮跟蹤器的跟蹤寬度、跟蹤深度、存儲器容量、精度指標要求等條件來決定需要采用的外部時鐘的大小;計數器輸出與預置寄存單元的輸出同步進入運算單元,通過組合邏輯生成運算后的讀寫地址輸入地址控制單元;地址控制單元控制讀和寫兩路地址,它們分別為C+(P-DP-T)和C,這樣,讀地址和寫地址之間相差P-DP-T個時鐘節拍,可以看到在這里脈沖前沿被前移了DP+T的長度;輸入信號進入波門形成單元后,通過組合邏輯生成一個與輸入脈沖信號前沿同步、脈寬固定為一個時鐘節拍Wt的同步脈沖作為動態存儲器的data輸入,存儲器在讀/寫使能信號和讀/寫時鐘控制下得到Q輸出,在原理圖中還可看到容差也輸人了波門形成單元,通過組合邏輯將Q輸出的后沿后移2倍的DP長度,這樣,最終得到的輸出波門“沿”特性較輸入脈沖前沿提前DP+T,寬度特性為2(DP+1)Wt,可以看到,通過控制Wt、DP和T的取值,可得到指標允許范圍內的脈沖前沿可控的一定寬度的理想輸出跟蹤波門。

2、 設計應用

2.1 軟件操作平臺的要求

模塊化的數字式重復頻率跟蹤器對軟件操作平臺的要求主要包括:Windows 2000操作系統;Quartus2.0或以上版本;Microsoft Visual C++6.0應用軟件和自行編制的跟蹤器參數預置程序。

2.2 關于跟蹤器電路芯片的選擇

本設計中介紹的跟蹤器主要技術參數為:跟蹤信號個數為一路,脈沖信號重復周期范圍為20μs~5 000μs,容差參數寬度10 bit,提前量參數寬度6 bit,跟蹤精度為1μs,由此不難得出此跟蹤器的寬度要求為13 bit。

因為本跟蹤器設計中的關鍵器件為存儲器,所以,在FPGA器件的選擇上,應該重點考慮它的內部存儲器資源。由前述可知,每實現一路信號跟蹤需要2片存儲器參與工作,每片存儲器的寬度為1 bit,深度為13 bit,由此可知每實現一路信號跟蹤需要的存儲器容量為16 kB,這樣,就需要仿制出一個8 kB容量的存儲器模塊。同時,我們選擇的FPGA芯片的內部存儲器資源容量必須不小于16 kB才能夠實現對一路信號的實時跟蹤,而且,這是在理想狀態下的汁算所得,在實際應用中,考慮到FPGA器件的資源分配特性,不應該將資源滿額運轉,必須保留有一定的資源優化空間才能保證芯片的最佳工作狀態。所以,在芯片的選擇上,應該選擇一款內部存儲器資源容量較大于16 kB的芯片。依據Altera公司提供的開發軟件Quartus4.1,在Megawizard向導中的存儲器編譯管理器中,我們自行創建了一個寬度為1 bit、深度為13 bit、帶讀寫控制的存儲器模塊,并成功地替代且實現了原分立電路下的關鍵器件一存儲器所完成的全部功能,為數字式重復頻率跟蹤器的模塊化實現走出了最關鍵的一步。另外,如果希望實現對多路信號的跟蹤,就需要選擇內部存儲器資源容量更大的芯片,具體的選擇依據同前面所述。

Altera公司是一家專業的FPGA生產廠家,根據Altera公司提供的技術資料,該公司生產的APEX20K系列芯片EP20K30E系列至EP20K200E系列的內部存儲器資源大小從24 576 bit至106 496 bit不等,經過綜合比較,選擇了EP20K100QC240芯片,它的內部存儲器資源容量可以滿足對一路信號實施跟蹤時所需的存儲器資源要求。關于芯片的選型請參考Altera公司的相關資料。

目前,Altera公司生產的StratixⅡ系列芯片的最大內部存儲器資源容量為7 427 520 bit(參見Altera公司器件手冊),7 427 520 bit=7 Mbit,也就是說,從內部存儲器資源容量的角度出發,理論上,在分辨率為1μs、跟蹤信號寬度為1 bit的情況下,一片StraTIxⅡ系列的EPlS80型號的芯片存儲深度可以達到7 Mbit。

2.3 總線協議及時序

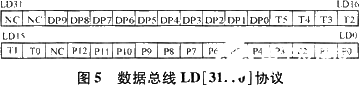

根據跟蹤器參數沒置需要,數據總線LD[31..0]協議如圖5所示。

其中,P0~P12為脈沖重復周期碼,T0~T5為提前量碼,DP0~DP9為容差碼,它們的計算精度均為1μs。

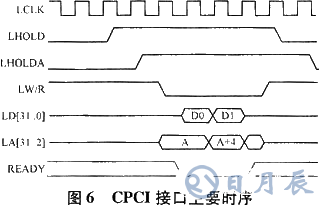

關于CPCI接口的主要時序關系見圖6。

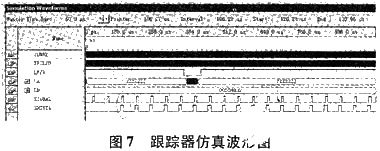

在Quartus4.1環境下,根據構建的FPGA邏輯電路,可以對跟蹤器進行時序仿真,其仿真結果見圖7。圖中標注處為輸入信號對應的輸出波門,因為電路中引入了二級數字延時器,所以輸出波門較輸入信號延遲了2個信號周期。

2.4 FPGA的配置芯片

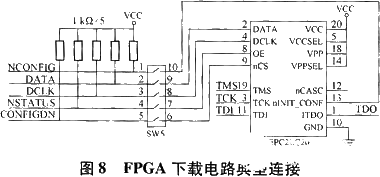

FPGA配置芯片的選擇主要根據FPGA配置文件的大小,同時參考FPGA生產廠家器件手冊的推薦配置用法。幾種常用的配置芯片容鼉大小如下:EPC2為1.6 Mbit,EPC4為4 Mbit,EPC8為8 Mbit,EPC16為16 Mbit,本跟蹤器選擇了EPC2Lc20芯片,它對應的下載電路連接方式參見圖8。

2.5 跟蹤器參數預置程序

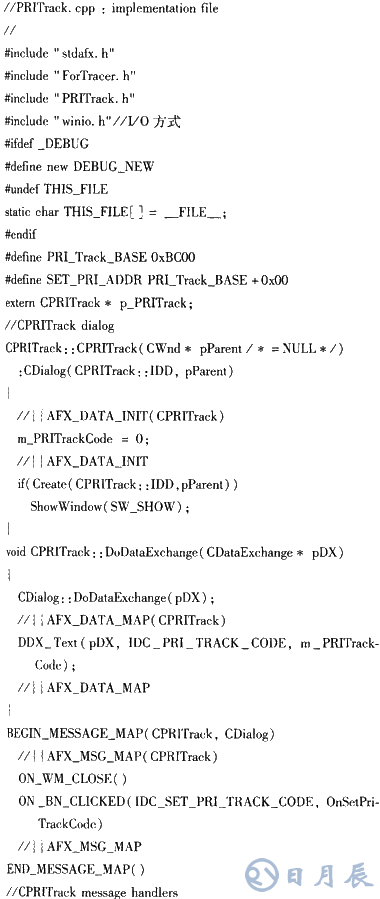

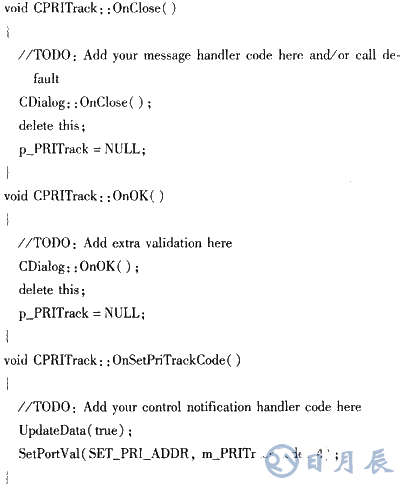

為了配合跟蹤器的檢驗,可以在VC6.0環境下自行編制一個小型的跟蹤器參數置數程序。

部分程序段格式及內容如下:

3、 結束語

本數字式重復頻率跟蹤器實現了在時域相關的基礎上對一批相同重復頻率脈沖信號的實時跟蹤,通過改變各個功能模塊的接口參數和對組合邏輯局部調整,可以得到電路特性指標允許范圍內的理想的跟蹤輸出波門。未來的發展方向可以關注以下幾點:脈寬相關、相位相關、可跟蹤的信號批數(多批)、可跟蹤的信號重復頻率類型(重復頻率P固定、抖動及參差)、對不同頻率和不同方位信號的跟蹤、跟蹤波門精度的提高等。從而使跟蹤器能夠在密集信號環境中快速、準確地產生各種復雜信號的跟蹤輸出信號,實現對多批不同頻率、不同方位、不同類型的目標分別進行有效實時跟蹤的目的。