由于PCB板上的電子器件密度越來越大,走線越來越窄,走線密度也越來越高,信號的頻率也越來越高,不可避免地會引入EMC(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析以及應(yīng)用就非常重要了。但目前國內(nèi)國際的普遍情況是,與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。同時,EMC仿真分析目前在PCB設(shè)計中逐漸占據(jù)越來越重要的角色。

PCB設(shè)計中的對EMC/EMI的分析目標信號完整性分析包括同一布線網(wǎng)絡(luò)上同一信號的反射分析,阻抗匹配分析,信號過沖分析,信號時序分析等等;對于鄰近布線網(wǎng)絡(luò)上不同信號之間的串擾分析。在信號完整性分析時還必須考慮布線網(wǎng)絡(luò)的物理拓撲結(jié)構(gòu),PCB介質(zhì)層的電介質(zhì)特性和介電常數(shù)以及每一布線層的電氣特性。現(xiàn)在已經(jīng)有了抑制電子設(shè)備和儀表的EMI的國際標準,統(tǒng)稱為電磁兼容(EMC)標準,它們可以作為PCB設(shè)計者布線和布局時抑制電磁輻射和干擾的規(guī)則,對于軍用電子產(chǎn)品設(shè)計者來說,標準會更嚴格,要求更苛刻。對于由多塊PCB板通過總線連接而成的系統(tǒng),還必須分析不同PCB板之間的電磁兼容性能以及接口電路和連接器的EMC/EMI性能。

EMC/EMI的仿真需要用到仿真模型EMC/EMI分析要了解所用到的元器件的電氣特性,之后才能更好地具體模擬仿真。目前應(yīng)用較多的有IBIS和SPICE模型。IBIS(I/O Buffer Interface Specification),即ANSI/EIA-656,是一種通過測量或電路仿真得到,基于V/I曲線的I/O緩沖器的快速而精確描述電氣性能的模型。

1990年由INTEL牽頭、聯(lián)合數(shù)家著名的半導(dǎo)體廠商共同制定了IBIS V1.0的行業(yè)標準,經(jīng)過不斷的完善和發(fā)展,于1997年更新為IBIS V3.0.現(xiàn)在此標準已被NS、Motorola、TI、IDT、Xilinx、Siemens、Cypress、VLSI等數(shù)百家半導(dǎo)體廠商支持,同時Cadence、Mentor、Incases、Zuken-Redac等RDA公司在各自的軟件中也添加了有關(guān)IBIS的功能模塊。

IBIS文件是一種文本文件,是通過標準軟件格式生成的“行為”信息的描述,以說明IC的模擬電氣特性。IC的SPICE模型是各半導(dǎo)體廠商的商業(yè)秘密,受到知識產(chǎn)權(quán)的保護,而IBIS模型是對用戶完全開放的數(shù)據(jù),所以設(shè)計者可以比較容易得到IBIS模型。當然,如果有SPICE模型,IBIS模型可以從SPICE模型來生成。目前,一般都可以從器件廠商那里拿到IBIS模型。

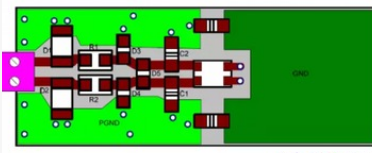

應(yīng)用EMC/EMI仿真來提高PCB設(shè)計的質(zhì)量在PCB布局布線結(jié)束后,將GERBER文件做成電路板之前對電路設(shè)計進行EMC/EMI的分析和模擬仿真。同時依據(jù)實際電路的動態(tài)工作頻率分析信號的強度、時延等特性。如果設(shè)計的PCB中含有與外部的接口,IC上外加了散熱器或電路本身功耗大時,必須進一步進行電磁輻射的模擬仿真分析。對于高速電路有必要進行布線網(wǎng)絡(luò)的傳輸線分布參數(shù)分析。

EDA開發(fā)廠商也漸漸意識到用戶在EMC/EMI模擬仿真領(lǐng)域的需求,德國的INCASES公司為設(shè)計者提供了EMC/EMI模擬仿真分析的軟件包EMC-WORKBENCH,成為該行業(yè)的領(lǐng)袖并多次主持了IEEE在EMC/EMI方面的研討會。EMC-WORKBENCH能夠滿足電路設(shè)計者在電磁兼容方面的迫切需求,改進了PCB設(shè)計的流程,簡化后期硬件調(diào)試中許多繁雜的工作。

同時,IC內(nèi)部也要充分考慮到EMC/EMI的問題。目前,大部分芯片廠商都會處理好IC內(nèi)部的EMC/EMI的問題。但廣大的設(shè)計者也應(yīng)當留意芯片中可能存在的問題,同時將EMC/EMI的解決在板極上做到極致。

電子工程師們可以利用仿真工具,并有效綜合設(shè)計經(jīng)驗,可以更好地提高產(chǎn)品的質(zhì)量和產(chǎn)品的可靠性。

來源;互聯(lián)網(wǎng)