在進行比較復(fù)雜的板子設(shè)計的時候,你必須進行一些設(shè)計權(quán)衡。因為這些權(quán)衡,那么就存在一些因素會影響到PCB的電源分配網(wǎng)絡(luò)的設(shè)計。

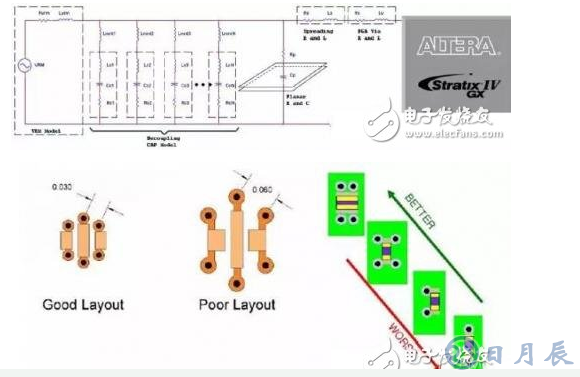

當電容安裝在PCB板上時,就會存在一個額外的回路電感,這個電感就與電容的安裝有關(guān)系。回路電感值的大小是依賴于設(shè)計的。回路電感的大小取決于電容到過孔的這段線的線寬和線長,走線的長度即連接電容和電源/地平面長度,兩個孔間的距離,孔的直徑,電容的焊盤,等等。如圖1所示為各種電容的安裝圖形。

圖1 最佳的和最差的電容布局

減小電容回路電感的設(shè)計要點:

■孔要放在離電容盡可能近的地方。減小電源/地的孔間距。如果可以,用多對電源/地孔并聯(lián)在一起。諸如電流極性相反的兩個孔放置的盡量近,電流極性相同的孔放置的盡量遠。

■用短而寬的走線來連接孔和電容引腳。

■把電容擺放在PCB的表面(頂層和底層)盡量靠近他們相應(yīng)的電源/地平面。這樣能減小孔之間的距離。在電源/地之間用薄的電解質(zhì)。

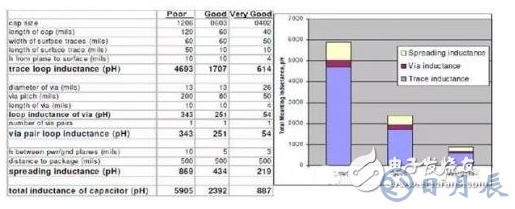

接下來是三種不同情況的設(shè)計,對于電容的安裝和傳播電感。圖2表示的是各種設(shè)計情況對回路電感量的引入情況。

圖2 設(shè)計情況

情況1-差的設(shè)計

■設(shè)計人員不關(guān)注電源分配網(wǎng)絡(luò)(PDN)的設(shè)計。

■孔的間距沒有優(yōu)化。

■電源和地平面間的距離沒有優(yōu)化。

■孔到電容引腳之間的走線距離較長。

對于整個回路電感大小來講,回路電感主要來自所布的線,因為與其它兩種情況比較,差的設(shè)計時的線長是它們(好的設(shè)計和非常好的設(shè)計)的5倍。從安裝電容的底層到最近平面的距離也是回路電感大小的主要因素。因為這是沒有優(yōu)化的(10mil),走線對整個回路電感大小的影響是非常大的。同樣,因為設(shè)計人員在電源和地之間用了10mil的電介質(zhì)材料,那么回路電感的次要因素來自傳播電感。過孔間的距離沒有優(yōu)化的效果相對于小孔的長度就沒有那么的顯著。孔的影響在比較長的過孔時會變得更大。

情況2-好的設(shè)計

■設(shè)計人員關(guān)注了部分電源分配網(wǎng)絡(luò)(PDN)的設(shè)計。

■孔的間距有所改善。孔的長度保持不變。

■電源和地平面間的距離有所改善。

■過孔到電容引腳之間的走線距離經(jīng)過了優(yōu)化。

走線的回路電感依然還是整個回路電感的主要貢獻者。但是,好的設(shè)計的走線回路電感要比差的設(shè)計情況的的走線回路電感小2.7倍左右。因為設(shè)計人員減小了電介質(zhì)的厚度,從10mil減小到了5mil,傳播電感減小了一半。由于減小了過孔間的距離,過孔的影響有了一點點改善。

情況3-非常好的設(shè)計

■設(shè)計人員非常注重PDN的設(shè)計。

■孔的間距和長度都有改善。

■電源和地之間的距離也進行了充分的優(yōu)化。

■ 過孔到電容引腳之間的走線距離經(jīng)過了優(yōu)化。

非常好的設(shè)計的走線的電感比差的設(shè)計的走線電感要小大約7.65倍。由于減少了走線長度,在PCB板上減少了從電容安裝的底層表面到最近的平面層的厚度,這就達到了目的。由于設(shè)計人員已經(jīng)優(yōu)化了電源和地之間的電解質(zhì)層厚度,傳播電感就會大大的減小。由于孔間距和孔長度大大的減小,那么過孔的回路電感也得到了顯著改善。相比差的設(shè)計,由于7個主要因素的其中之一減少,非常好的設(shè)計情況的總回路電感就被減少了。。

在PCB板上,額外的過孔回路電感通過安裝電容被引入,這樣就降低電容的諧振頻率。當你在設(shè)計電源分配網(wǎng)絡(luò)(PDN)時,必須要考慮到這個因素。在高頻設(shè)計的時候,減小回路電感是降低阻抗的唯一能看得見的方法。

對于給定的電源,相比較非常好的設(shè)計和差的設(shè)計情況,PDN工具產(chǎn)生的報告顯示非常好的設(shè)計的PCB截止頻率會更高。這也許與預(yù)期的結(jié)果是相反的,因為相對于對低截止頻率的去耦,對較高截止頻率的去耦需要更多的電容。

對于非常好的設(shè)計的情況,較高的截止頻率意味著能對較高頻率進行去耦。擺放在PCB板上的電容對噪聲直到一個較高頻都有去耦效果。

對于差的設(shè)計的情況,對超過較低截止頻率的PCB板不能去耦。任何額外的電容增加,即增加超過截止頻率的去耦電容只能增加BOM成本而對去耦效果沒有任何影響。相對于非常好的設(shè)計,對于差的這種設(shè)計情況,其電源分配網(wǎng)絡(luò)的設(shè)計對于某一特定頻率的噪聲更容易受到影響

作為另外一個例子,假設(shè)一塊20層的PCB板總共有115mil的厚度。電源層在第3層。從第一層(FPGA在的這一層)到第3層的厚度有12mil。那么從底層到第3層的厚度就是103mil。電源和地層被3mil后的電介質(zhì)分離開。對于這種軌跡的BGA孔的電感大小為5nH(對于這種電源軌跡5對孔)。為了應(yīng)對第一層比較緊密的布局布線區(qū)域,與之相關(guān)聯(lián)的去耦電容都安裝在底層。由于這樣安裝會有很長的過孔,這種權(quán)衡設(shè)計導(dǎo)致了很高的電容安裝電感值。經(jīng)過充分優(yōu)化后,0402封裝的電容在底層的安裝電感是2.3nH,而同樣的電容放在第一層的安裝電感是0.57nH。

為了改善這種給軌跡的PDN效果,你可以把一些高頻電容放置在第一層,同時把中頻和bulk電容還是放在原來的位置上即底層。這種電路設(shè)計對PDN是截止的解決方法,因為高頻電容是在截止頻率以下作為第一響應(yīng)的電容。電容的效果依賴于總的回路電感(電容的安裝電感+傳播電感+BGA孔的電感)與FPGA。你可以把高頻電容放在第一層并離FPGA稍微遠一點點的地方。電容放在FPGA breakout區(qū)域外的傳播電感是0.2nH。相對于原來放置在底層的方法,這種新的放置方法還是有益的,因為總的回路電感(0.57nH+0.2nH+0.05nH=0.82nH)比放置在底層的時候的總電感要小。

PCB板的傳播電感是與設(shè)計是相關(guān),電源和地平面間的介質(zhì)中它是均勻存在的。3mil厚度或者更薄的厚度是最佳的減小平面?zhèn)鞑ル姼械脑O(shè)計。你可以根據(jù)如下的設(shè)計指導(dǎo)來提升PDN的性能。

如下的是關(guān)于順序重要性的設(shè)計指導(dǎo),從第一層到底層—在第一層的設(shè)計指導(dǎo)是最重要的。

■減小電源和地層間電介質(zhì)厚度。當設(shè)計板子的疊層時,確定電源、層和其他的層。舉一個例子,如疊層PWR1 - GND1 - SIG1 - SIG2- GND2 - PWR2要優(yōu)于PWR1 - SIG1 - GND1 - SIG2 - GND2 - PWR2這種疊層。第二種情況的結(jié)果是沒有對電源和地之間的距離優(yōu)化的設(shè)計。這樣的設(shè)置會導(dǎo)致大電容傳播電感在PWR1/GND1之間比在PWR2/GND2之間的電感大。你可以在電源和地平面之間找到一種典型的3mil的電介質(zhì)厚度而不增加額外的成本。對于額外的性能改善,考慮比3mil更薄的電介質(zhì)厚度。但是,這會導(dǎo)致PCB的成本上升。

■當選定電容的時候,選擇多個電容值,而不是選擇一個相同值的大電容來達到目標阻抗。在PDN中,阻抗的峰值是由諧振反應(yīng)形成的。高ESR在諧振頻率點能抑制諧振,因此減少阻抗峰值的高度。在電容的諧振頻率處和阻抗峰值處,用一些電容值相同的電容能截止的減少ESR。

在一個很寬的頻率范圍內(nèi),選擇多種電容值的電容種類,能維持一個相對高的ESR。

■選擇放置高頻電容的位置,以減少整個回路電感。整個電感是由電容的ESL、安裝電感、傳播電感和BGA的過孔電感組成的。在放置電容時優(yōu)先放置高頻電容,其次是中頻和低頻電容。

■當在分割平面時,確保平面的形狀成適當?shù)姆叫巍1苊猹M長的平面形狀,因為這樣做會限制電流的大小和增加平面的傳播電感。

■中頻和低頻的電容對于如何放置沒有那么的敏感。可以把他們放在離FPGA稍微遠一點的地方。

權(quán)衡多路設(shè)計的情況

在一塊有多路外設(shè)的PCB板上,你的設(shè)計就不能再共享一個供電電源。這也許需要你通過你的設(shè)計去執(zhí)行DDR的電源接口,聯(lián)合各種I/O口的電源軌跡,或者聯(lián)合各種接收端的電源軌跡以減少PCB的BOM成本和PCB的布局復(fù)雜度。

電源軌跡共享增加了PDN的復(fù)雜度,同時在PCB上和die的位置處也增加了大量的噪聲。對于多路的情況,設(shè)計電源的分配解決方法主要有兩步:

1 低頻解決方法

2 高頻解決方法

在非常低頻的時候,第一步確保VRM的大小是否適合處理各種電流的需要。