引 言

基于提升框架的小波變換方法,利用FPGA 可編程特性可實(shí)現(xiàn)多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結(jié)構(gòu)能有效地計(jì)算DWT。對(duì)于較長(zhǎng)的濾波器,LS 的操作次數(shù)比濾波器組的操作方式減少將近一半,更適合硬件實(shí)現(xiàn)。作者根據(jù)提升小波變換的框架式結(jié)構(gòu),利用FPGA 可完全重構(gòu)的特點(diǎn)構(gòu)造不同的小波變換核,以滿足不同應(yīng)用場(chǎng)合的要求。在結(jié)構(gòu)設(shè)計(jì)中采用由下至上的設(shè)計(jì)方法,每個(gè)提升步驟都由一些可編程的參數(shù)來(lái)表示,保證了每個(gè)步驟均可重構(gòu)。這些參數(shù)包括用于表示數(shù)據(jù)的位數(shù)和每個(gè)內(nèi)部數(shù)學(xué)模塊的通道深度。在邏輯綜合時(shí)按不同小波的要求,改變參數(shù)可得到不同的結(jié)果。以圖像處理中常用的(5 ,3)濾波器為例說(shuō)明依靠FPGA 的重組特性實(shí)現(xiàn)濾波器的小波變換核方法。實(shí)驗(yàn)結(jié)果表明,利用FPGA 設(shè)計(jì)的提升小波變換核能滿足不同場(chǎng)合和不同運(yùn)行的要求。

LS 小波變換理論

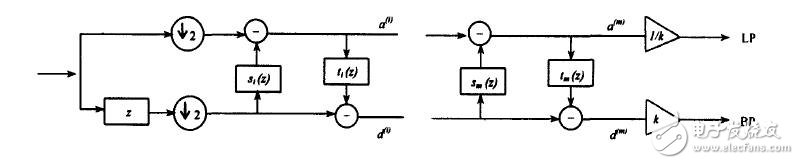

LS 變換過(guò)程如圖1 所示,逆變換與正變換相同,只是順序相反。時(shí)間離散的濾波器可由它的多項(xiàng)矩陣來(lái)表示,多項(xiàng)矩陣由脈沖響應(yīng)的奇偶采樣序列的Z 變換得到。LS 小波變換的實(shí)質(zhì)是對(duì)經(jīng)典小波濾波器采用Euclidean 算法的多項(xiàng)式進(jìn)行分解。

圖1 正向LS 變換

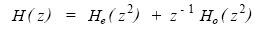

一個(gè)時(shí)間離散的濾波器H( z ) 用多項(xiàng)式表示如下:

He ( z ) 和Ho ( z ) 各自從

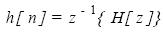

奇偶系數(shù)得到。分析濾波器H ( z ) 和G( z ) 分別表示低通和高通,表示成多相矩陣為

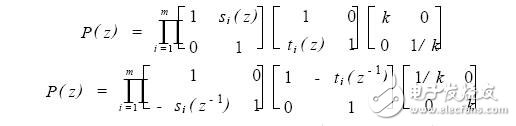

P( z ) 可被模擬為分析濾波器。根據(jù)Euclidean算法可將P( z ) 和P( z ) 分解成:

上面的分解不是唯一的,可有幾對(duì){ si ( z ) } 和{ t i ( z ) } 濾波器,但對(duì)于計(jì)算DWT 所有的選擇是等同的。

FPGA 及提升核的實(shí)現(xiàn)

FPGA 及重構(gòu)特性

FPGA(Field Programmable Gate Array ,現(xiàn)場(chǎng)可編程門陣列) 是超大規(guī)模集成電路(VL、SI) 技術(shù)和計(jì)算機(jī)輔助設(shè)計(jì)(CAD) 技術(shù)發(fā)展的結(jié)果。FPGA 器件集成度高、體積小、具有通過(guò)用戶編程實(shí)現(xiàn)專門應(yīng)用的功能。FPGA 一般由3 種可編程電路和1 個(gè)用于存放編程數(shù)據(jù)的SRAM 組成。這3 種可編程電路是:可編程邏輯塊CLB (Configurable Logic Block) 、輸入/輸出模塊IOB ( I/O Block) 和互連資源IR( Interconnect Resource) 。由于基于小波的應(yīng)用越來(lái)越廣泛,所以利用FPGA 的靈活結(jié)構(gòu)實(shí)現(xiàn)可重構(gòu)的提升框架小波變換核具有很高的應(yīng)用價(jià)值和研究?jī)r(jià)值。設(shè)計(jì)從基本的數(shù)學(xué)模塊和邏輯模塊開始,采用由下至上的設(shè)計(jì)方法,所有的庫(kù)模塊用VHDL 語(yǔ)言描述,允許根據(jù)設(shè)計(jì)精度要求選擇每個(gè)單元的數(shù)據(jù)通道大小。為了滿足不同環(huán)境的需要,既要求可以改變單獨(dú)模塊的通道層深度,又要求考慮與其他設(shè)備的相容性。將提升方法與FPGA 的特性結(jié)合起來(lái),使不同的提升小波變換在FPGA 上可滿足不同應(yīng)用場(chǎng)合的需要。

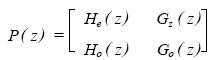

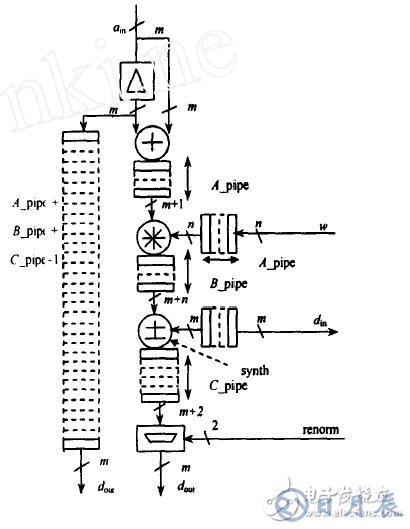

圖2 提升核結(jié)構(gòu)體

提升小波變換核的實(shí)現(xiàn)

如圖1 所示,LS 變換是連續(xù)的獨(dú)立的簡(jiǎn)單濾波操作過(guò)程,這個(gè)過(guò)程就是提升步驟。由圖1 可導(dǎo)出優(yōu)化了的提升核結(jié)構(gòu)體。近幾年,采用JPEG2000 標(biāo)準(zhǔn)進(jìn)行圖像傳輸成為熱點(diǎn),很多文獻(xiàn)中均提出了不同的提升小波變換結(jié)構(gòu)體。

但是這些提升結(jié)構(gòu)體大都只考慮可操作性,而忽略了功耗和靈活性。作者提出的提升核結(jié)構(gòu)體(圖2) 采用與以往不同的由下至上的設(shè)計(jì)方法。主要特點(diǎn)是指定了1 個(gè)單獨(dú)的流水式的乘法單元和2個(gè)加法單元。乘法單元主要用于處理濾波器系數(shù)的對(duì)稱問(wèn)題,加法單元用于實(shí)現(xiàn)分析或綜合的變換。

值得注意的是所有的通道層都可用所設(shè)計(jì)的庫(kù)模塊來(lái)排列,因此為了保證內(nèi)部IP 核數(shù)據(jù)流的同步性,必須考慮前后交叉問(wèn)題。例如,在加法輸出時(shí),已經(jīng)放置了一個(gè)乘法器,允許對(duì)提升步驟的結(jié)果進(jìn)行歸一化。采用這種設(shè)計(jì)方法,能獲得最高的數(shù)據(jù)精度和最快的運(yùn)行速度。此外,整數(shù)的數(shù)學(xué)單元更容易進(jìn)行深層的流水操作,獲得很高的數(shù)據(jù)吞吐量。圖2 所提出的結(jié)構(gòu)既考慮了可操作性又考慮了應(yīng)用的靈活性,由于提高了運(yùn)行速度,所以降低了功耗。

邏輯綜合結(jié)果

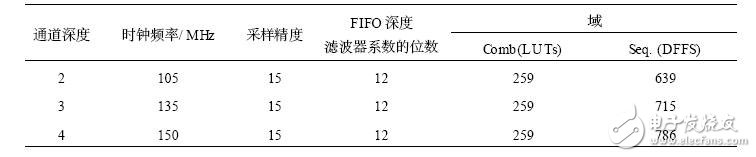

首先采用VHDL 語(yǔ)言來(lái)描述由基本的可重構(gòu)的數(shù)學(xué)模塊和邏輯模塊設(shè)計(jì)的變換核結(jié)構(gòu)體,然后在MAX+PLUSⅡ集成環(huán)境下進(jìn)行功能仿真,實(shí)現(xiàn)所需變換核,最后進(jìn)行FPGA 邏輯綜合。在Altera1 公司的FLEX10K上設(shè)計(jì)的結(jié)構(gòu)體,經(jīng)過(guò)邏輯綜合得到很滿意的結(jié)果,見表1 。表1 的結(jié)果直接由邏輯綜合得到,沒有考慮各種客觀因素引起的延時(shí)。在設(shè)計(jì)流程步驟之后的安放運(yùn)行過(guò)程中,可進(jìn)行更精確的時(shí)序分析。另外,為了獲得完整的分析結(jié)果,需參考FPGA 廠家提供的指標(biāo)估計(jì)功率消耗,使用時(shí)應(yīng)選擇功耗小的可編程器件,更好地滿足不同使用環(huán)境的要求。以(5 ,3) 濾波器為例,計(jì)算(5 ,3) 小波需要4個(gè)提升核的疊加,所提出的結(jié)構(gòu)體計(jì)算正向或逆向(5 ,3)DWT ,對(duì)每幀像素1400×1400 采用15位采樣數(shù)和12位合成濾波器系數(shù),以全時(shí)鐘頻率運(yùn)行,進(jìn)行5 層分解、重構(gòu),每秒鐘能處理25 幀圖像,功耗為267.6 mW。

表1 提升核綜合結(jié)果

結(jié)束語(yǔ)

提出的可重構(gòu)的提升核結(jié)構(gòu)體,采用特殊的即從下至上的設(shè)計(jì)方法,保證了最大限度地重復(fù)利用性和重構(gòu)特性。仿真結(jié)果說(shuō)明,提升小波變換核的結(jié)構(gòu)體無(wú)論在處理能力和功耗方面都取得了很好的結(jié)果,尤其在處理速度上,能滿足圖像處理實(shí)時(shí)性要求。將來(lái)的進(jìn)一步發(fā)展是將更多的自由參數(shù)加入基本的算術(shù)模塊中,保證結(jié)構(gòu)體具有更好的操作性,并且使功率消耗減少,能滿足不同應(yīng)用場(chǎng)合的需要,對(duì)降低設(shè)備成本,提高使用效率有實(shí)際意義。