引 言

縱觀電子行業(yè)的發(fā)展,1992年只有40%的電子系統(tǒng)工作在30 MHz以上,而且器件多使用DIP、PLCC等體積大、引腳少的封裝形式;到1994年,已有50%的設(shè)計(jì)達(dá)到了50 MHz的頻率,采用PGA、QFP、RGA等封裝的器件越來越多;1996年之后,高速設(shè)計(jì)在整個(gè)電子設(shè)計(jì)領(lǐng)域所占的比例越來越大,100 MHz以上的系統(tǒng)已隨處可見,采用CS(線焊芯片級(jí)BGA)、FG(線焊腳距密集化BGA)、FF(倒裝芯片小間距BGA)、BF(倒裝芯片.BGA)、BG(標(biāo)準(zhǔn)BGA)等各種BGA封裝的器件大量涌現(xiàn),這些體積小、引腳數(shù)已達(dá)數(shù)百甚至上千的封裝形式已越來越多地應(yīng)用到各類高速、超高速電子系統(tǒng)中。

從IC芯片的發(fā)展及封裝形式來看,芯片體積越來越小、引腳數(shù)越來越多;同時(shí),由于近年來IC工藝的發(fā)展,使得其速度也越來越高。這就帶來了一個(gè)問題,即電子設(shè)計(jì)的體積減小導(dǎo)致電路的布局布線密度變大,而同時(shí)信號(hào)的頻率還在提高,從而使得如何處理高速信號(hào)問題成為一個(gè)設(shè)計(jì)能否成功的關(guān)鍵因素。隨著電子系統(tǒng)中邏輯復(fù)雜度和時(shí)鐘頻率的迅速提高,信號(hào)邊沿不斷變陡,印刷電路板的線跡互連和板層特性對(duì)系統(tǒng)電氣性能的影響也越發(fā)重要。對(duì)于低頻設(shè)計(jì),線跡互連和板層的影響可以不考慮,但當(dāng)頻率超過50 MHz時(shí),互連關(guān)系必須考慮,而在*定系統(tǒng)性能時(shí)還必須考慮印刷電路板板材的電參數(shù)。因此,高速系統(tǒng)的設(shè)計(jì)必須面對(duì)互連延遲引起的時(shí)序問題以及串?dāng)_、傳輸線效應(yīng)等信號(hào)完整性(Signal Integrity,SI)問題。

當(dāng)硬件工作頻率增高后,每一根布線網(wǎng)絡(luò)上的傳輸線都可能成為發(fā)射天線,對(duì)其他電子設(shè)備產(chǎn)生電磁輻射或與其他設(shè)備相互干擾,從而使硬件時(shí)序邏輯產(chǎn)生混亂。電磁兼容性(Electromagnetic CompaTIbility,EMC)的標(biāo)準(zhǔn)提出了解決硬件實(shí)際布線網(wǎng)絡(luò)可能產(chǎn)生的電磁輻射干擾以及本身抵抗外部電磁干擾的基本要求。

1 高速數(shù)字電路設(shè)計(jì)的幾個(gè)基本概念

在高速數(shù)字電路中,由于串?dāng)_、反射、過沖、振蕩、地彈、偏移等信號(hào)完整性問題,本來在低速電路中無需考慮的因素在這里就顯得格外重要;另外,隨著現(xiàn)有電氣系統(tǒng)耦合結(jié)構(gòu)越來越復(fù)雜,電磁兼容性也變成了一個(gè)不能不考慮的問題。

要解決高速電路設(shè)計(jì)的問題,首先需要真正明白高速信號(hào)的概念。高速不是就頻率的高低來說的,而是由信號(hào)的邊沿速度決定的,一般認(rèn)為上升時(shí)間小于4倍信號(hào)傳輸延遲時(shí)可視為高速信號(hào)。即使在工作頻率不高的系統(tǒng)中,也會(huì)出現(xiàn)信號(hào)完整性的問題。這是由于隨著集成電路工藝的提高,所用器件I/O端口的信號(hào)邊沿比以前更陡更快,因此在工作時(shí)鐘不高的情況下也屬于高速器件,隨之帶來了信號(hào)完整性的種種問題。

2 高速數(shù)字電路設(shè)計(jì)的基本要求

在PCB設(shè)計(jì)中,電磁兼容性的分析也離不開布線網(wǎng)絡(luò)本身的信號(hào)完整性,主要分析實(shí)際布線網(wǎng)絡(luò)可能產(chǎn)生的電磁輻射和電磁干擾,以及電路板本身抵抗外部電磁干擾的能力,并且依據(jù)設(shè)計(jì)者的要求提出布局和布線時(shí)抑制電磁輻射和干擾的規(guī)則,作為整個(gè)PCB設(shè)計(jì)過程的指導(dǎo)原則。電磁輻射分析主要考慮PCB板與外部接口處的電磁輻射、PCB板中電源層的電磁輻射以及大功率布線網(wǎng)絡(luò)動(dòng)態(tài)工作時(shí)對(duì)外的輻射問題。對(duì)于高速數(shù)字電路設(shè)計(jì),尤其是總線上數(shù)字信號(hào)速率高于50 MHz時(shí),以往采用集總參數(shù)的數(shù)學(xué)模型來分析EMC/EMI特性顯得無能為力,設(shè)計(jì)者們更趨向于采用分布離散參數(shù)的數(shù)學(xué)模型做布線網(wǎng)絡(luò)的傳輸線分析(TALC)。對(duì)于多塊PCB板通過總線連接而成的電子系統(tǒng),還必須分析不同PCB板之間的電磁兼容性能。

針對(duì)高速數(shù)字電路設(shè)計(jì)中的電磁兼容性和信號(hào)完整性問題,在進(jìn)行高速PCB板設(shè)計(jì)時(shí)需要從以下一些方面進(jìn)行考慮。

2.1 端接匹配

由源端與負(fù)載端阻抗不匹配導(dǎo)致的傳輸線上阻抗不連續(xù),會(huì)引起信號(hào)線上的反射,負(fù)載將一部分電壓反射回源端,造成電平的抬高,對(duì)器件產(chǎn)生破壞性的影響。同時(shí),由于任何傳輸線上都存在固有的電感和電容,如果信號(hào)在傳輸線上來回反射,必然會(huì)產(chǎn)生振鈴和環(huán)繞振蕩現(xiàn)象,引起電路時(shí)序的失調(diào)。采用源端或終端的端接匹配是一個(gè)比較好的解決方法。

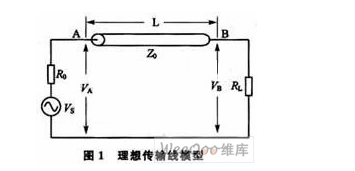

用圖1所示的理想傳輸線模型來分析與信號(hào)反射有關(guān)的重要參數(shù)。圖中,理想傳輸線L被內(nèi)阻為R0的數(shù)字信號(hào)驅(qū)動(dòng)源Vs驅(qū)動(dòng),傳輸線的特性阻抗為Z0,負(fù)載阻抗為RL。

負(fù)載端阻抗與傳輸線阻抗不匹配會(huì)在負(fù)載端(B點(diǎn))反射一部分信號(hào)回源端(A點(diǎn)),反射電壓信號(hào)的幅值由負(fù)載反射系數(shù)ρL決定:

式中ρL稱為負(fù)載電壓反射系數(shù),它實(shí)際上是反射電壓與入射電壓之比。

由式(1)可見,-1≤ρL≤+1,且當(dāng)RL=Z0時(shí),ρL=0,這時(shí)就不會(huì)發(fā)生反射。即只要根據(jù)傳輸線的特性阻抗進(jìn)行終端匹配,就能消除反射。從原理上說,反射波的幅度可以大到入射電壓的幅度,極性可正可負(fù)。當(dāng)RLL《0,處于過阻尼狀態(tài),反射波極性為負(fù);當(dāng)RL》Z0時(shí),ρL》0,處于欠阻尼狀態(tài),反射波極性為正。

當(dāng)從負(fù)載端反射回的電壓到達(dá)源端時(shí),又將再次反射回負(fù)載端,形成二次反射波,此時(shí)反射電壓的幅值由源反射系數(shù)ρS決定:

傳輸線的端接通常采用兩種策略:負(fù)載端并行端接匹配、源端串行端接匹配。只要負(fù)載反射系數(shù)或源反射系數(shù)二者任一為零,反射都將被消除。并行端接在信號(hào)能量反射回源端之前在負(fù)載端消除反射,即使ρL=0,消除一次反射,這樣可以減小噪聲、電磁干擾(EMI)及射頻干擾(RFI);串行端接則是在源端消除由負(fù)載端反射回來的信號(hào),即使ρs=0和ρL=1(負(fù)載端不加任何匹配),只是消除二次反射,在發(fā)生電平轉(zhuǎn)移時(shí),源端信號(hào)會(huì)出現(xiàn)持續(xù)時(shí)間為2TD(TD為信號(hào)源端到終端的傳輸延遲)的半波波形,這意味著沿傳輸線不能加入其他信號(hào)輸入端,因?yàn)樵谏鲜?TD時(shí)間內(nèi)會(huì)出現(xiàn)不正確的邏輯態(tài)。兩種端接策略各有其優(yōu)缺點(diǎn),不過由于并行端接的匹配網(wǎng)絡(luò)需要與電源連接,使用較為復(fù)雜;串行端接只需要在信號(hào)源端串入一個(gè)電阻,消耗功率小而且易于實(shí)現(xiàn),有較大的實(shí)際工程應(yīng)用價(jià)值,所以被廣泛采用。

2.2 防止地彈

當(dāng)PCB板上的眾多數(shù)字信號(hào)同步進(jìn)行切換時(shí)(如CPU的數(shù)據(jù)總線、地址總線等),由于電源線和地線上存在阻抗,會(huì)產(chǎn)生同步切換噪聲(Simultaneous SwitchNoise,SSN)。與此同時(shí),由于芯片封裝電感的存在,在電路同步切換過程中形成的大電流涌動(dòng)會(huì)引起地平面的反彈噪聲(簡(jiǎn)稱為地彈),這樣在真正的地平面(0 V)上就要產(chǎn)生電壓的波動(dòng)和變化,這個(gè)噪聲會(huì)影響其他元器件的動(dòng)作。

SSN和地彈的強(qiáng)度也取決于集成電路的I/O特性、PCB板電源層和地平面層的阻抗以及高速器件在PCB板上的布局和布線方式,負(fù)載電容的增大、負(fù)載電阻的減小、地電感的增大、同時(shí)開關(guān)器件數(shù)目的增加均會(huì)導(dǎo)致地彈的增大。在高速PCB電路設(shè)計(jì)中可以采取以下一些基本措施來減小SSN和地彈的影響:

①降低輸出翻轉(zhuǎn)速度。一些新的總線驅(qū)動(dòng)器件采用內(nèi)嵌的電路設(shè)計(jì),在對(duì)傳輸延時(shí)影響最小的前提下,降低翻轉(zhuǎn)速度。

②采用分離的專門參考地。分離的參考地由于電流很小,地反射現(xiàn)象會(huì)大大減小。分離地的芯片要注意使每個(gè)地線能夠有直接到地平面的最短路徑。

③降低系統(tǒng)供給電源的電感。高速電路設(shè)計(jì)中要求使用單獨(dú)的電源層,并讓電源層和地平面盡量接近。

④降低芯片封裝中的電源和地引腳的電感。比如增加電源/地的引腳數(shù)目,減短引線長(zhǎng)度,盡可能采用大面積鋪銅。

⑤增加電源和地的互感。要讓電源和地的引腳成對(duì)分布,并盡量靠近。

⑥給系統(tǒng)電源增加旁路電容,這些電容可以給高頻的瞬變交流信號(hào)提供低電感的旁路,而變化較慢的信號(hào)仍然走系統(tǒng)電源回路。