處理器指令集架構(ISA)的代碼密度對在現實世界中的SoC處理器的能耗效率有很大的影響。在選擇嵌入式SoC處理器時,功耗和面積通常是主要被考慮的,但另一個主要因素,往往在這樣的評估中被忽視了:處理器指令集架構(ISA)的代碼密度。

一個緊密的指令集產生較小的代碼,導致少取指令。這對于能效有著重大的影響,因為從片上存儲器取指令所使用的能耗遠遠大于CPU執行指令所需的。

大多少? 2010年斯坦福大學詹姆斯·貝爾福的博士論文對高效的嵌入式計算研究表明,對于一個典型的32位RISC處理器,從一個2字節的片上緩存取指令所消耗的能量比一個32位的加法運算(在一個典型的45納米CMOS制程)多消耗的多6.8倍.

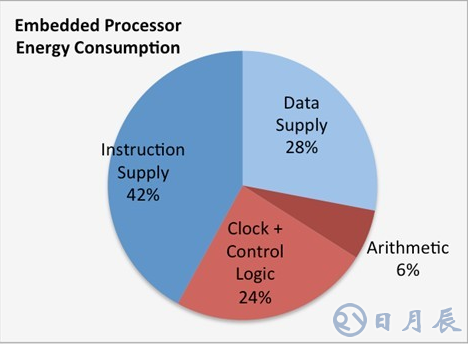

Dally等人的另一項發表在IEEE計算機的研究發現,典型的嵌入式處理器的能耗的42%來自取指,而只有6%的被消耗于執行實際的算術運算。這些研究都使用一個小的片上指令緩存。事實上指令往往更需要訪問較大的片上甚至片外存儲,那么功耗的影響將被放大, 系數6.8倍將變為50倍或更多。

這里的結論是明確的:使用需要較少指令的ISA,比簡單地選擇一個執行更有效的處理器在是節能上更有幫助.對一顆CPU而言, 面積(門使用)是另一種處理器選擇的常見標準。但SoC為程序存儲器所需的面積的要大得多,尤其是對非密集的代碼。

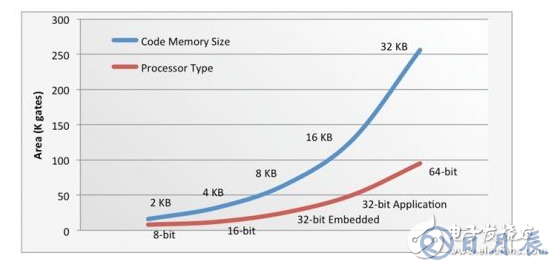

一般法則是約1千比特的片上SRAM占據的面積與1K的邏輯門相同。將此規則應用于一些典型的處理器所得的面積的結果,如圖2中曲線所示。 (在這里處理器的面積估計范圍從小型8位處理器的8K門到先進的64位處理器的100K門,而適合嵌入式程序的的片上代碼存儲空間估計范圍從2至32千字節。)

此圖清楚地表明,對大多數32位嵌入式SoC ,程序存儲器是CPU面積的兩倍或兩倍以上。更為緊湊的代碼顯然需要更小的程序存儲器。因此,在只考慮CPU所需門數的情況下, 選擇采用了緊湊ISA的處理器可以顯著降低SoC面積。

以上考慮促成了我們所提供的BA22系列的32位處理器內核,其對任何需要考慮低功耗的處理器系統都很有價值。我們相信BA22 ,在同行業中具有最優的代碼密度,估計比ARM ?的Thumb- 2 ISA的代碼密度最高能有20 %的提升。

有競爭力的性能( 2.1或以上Coremarks/兆赫) ,面積(15K門起), 時鐘頻率(在65nm - LP 將超過400 MHz)和功率效率(0.02毫瓦/兆赫茲),因為出眾的代碼密度,使得BA22成為功耗敏感的深嵌入系統CPU IP的最佳選擇之一。