FPGA設計者對非易失可重復編程FPGA解決方案的喜愛仍在延續,這種方案所需的相關額外費用并不太大 。設計人員對其的喜愛源于他們喜歡從一種產品中獲取多種能力,而迄今為止,只有非易失性解決方案能夠滿足他們的要求,因為它可以提供:最小的電路板面積和最簡單的系統集成、上電后能很快地獲取邏輯,以及最高的安全性。

事實上,除了這些傳統要求,在前兩代非易失FPGA產品的經驗基礎上,萊迪思半導體(Lattice Semiconductor)公司還認識到需要靈活的片上非易失存儲器,以及作為非易失FPGA新要求的用于現場邏輯更新的全面解決方案。

非易失FPGA的幾種方案

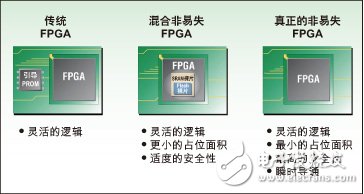

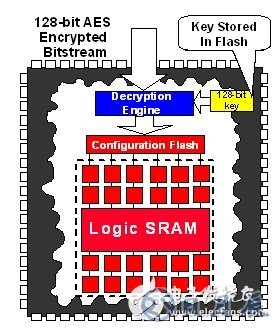

如今市場上有三種類型的FPGA:第一種是傳統的SRAM FPGA,系統上電時需要一個外部的非易失存儲器來配置FPGA;第二種是混合方法,把SRAM FPGA和非易失存儲器組合在單個封裝中;第三種常稱為真正的單片非易失FPGA,將非易失的單元嵌入在同一裸片上作為FPGA邏輯。如圖1所示,混合方法比SRAM方法好一些,而真正的非易失方法則是最佳方案,具有小尺寸、高安全性和上電時的瞬時運作。

非易失可重復編程FPGA的應用

在諸如通信、消費、計算、軍事和汽車等廣泛且多樣的終端市場中,非易失可重復編程FPGA被用來實現系統邏輯。非易失FPGA特別吸引那些要求減少部件數和占位面積,并迅速獲得邏輯或高安全性的應用。

1 小尺寸應用

這里所說的小尺寸應用包括:手持條碼掃描器、手持條碼閱讀器、智能電話、儀器與傳感器、航空電子設備等。傳統的 SRAM FPGA 需要一個引導存儲器,在上電時載入SRAM配置。有時候配置載入通過電路板上的微處理器來完成,而另外一些時候應用中需要一個獨立的引導存儲器。這兩個解決方案都不理想。從系統微處理器進行引導引入了額外的硬件和軟件間的相互依賴,還要求微處理器在FPGA配置前就運行,從而阻礙了其在系統中的核心功能。使用獨立的引導存儲器則增加了電路板的面積、元件,及相關成本。通過整合片上的引導存儲器,非易失FPGA提供了一個可選方案,也是更加完美的解決方案。

2 要求快速獲得邏輯的應用

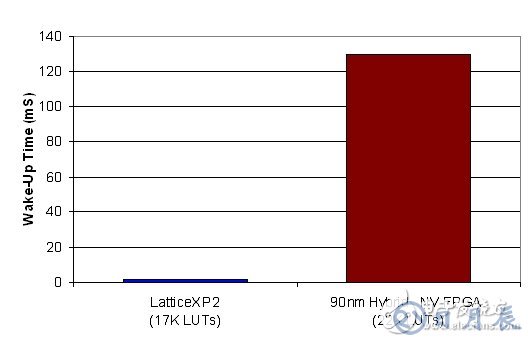

片上非易失存儲器能使器件在上電1毫秒內準備好運作,與SRAM和混合FPGA相比,SRAM和混合FPGA的配置需要數十或幾百毫秒。圖2為“喚醒時間”的差別。在許多常見應用中,真正的非易失FPGA所帶來的快速獲得邏輯的功能正是人們希望得到的特性。這些應用包括:即插即用總線接口(PCI, PCI Express, CAN)、上電復位控制、處理器總線譯碼、FPGA加載器、ASIC初始化以及使用工作循環的低功耗設計等。

圖1: 三種不同類型的FPGA

圖2 具有非易失FPGA的迅速獲得邏輯的能力

3 要求設計安全性的應用

在當今復雜的系統中,越來越多的FPGA被用來取代傳統上用ASIC和微處理器實現的功能。十年前,FPGA只是系統的外圍,而如今它是心臟。目前的FPGA工藝已使門數量達到幾百萬,FPGA成為非法盜版者的目標。FPGA設計者逐漸開始關注克隆、反向工程、過量生產、盜版服務等問題。

系統設計者使用的大多數SRAM FPGA需要在系統每次上電時由引導器件進行配置。引導器件和FPGA之間的連接存在很大的風險,因為配置數據暴露在外,易于在上電時被盜取。在封裝中嵌入非易失存儲器的混合方法對這種情況的改進有限。然而,相關的工具能夠免除封裝材料并獲得裸片的互連。真正的單片非易失器件沒有這樣的互聯,因此能夠提供絕佳的設計安全性。

除了設計被盜取或復制,在許多系統中很重要的是確保FPGA沒有被篡改。有這些要求的應用包括:信用卡讀卡器、自動出納機、武器系統以及游戲系統。

4 非易失存儲應用

由于非易失FPGA在密度和功能方面的水平繼續增強,許多設計者要在設計中整合非易失存儲器。這些需求分成兩種。

第一種是能整合小的獨立的EEPROM存儲器,在許多系統中存儲數據,例如電子ID碼、版本碼、日期打印、校準設置和資產ID。這種類型的存儲器不是經常通過串行接口訪問的。

第二種類型是能夠整合大的存儲塊,典型的應用為存儲數據,例如錯誤碼、上電自測試、數據查找表和微處理器碼。對數據的寫操作不是經常的,讀數據則是經常的,讀操作的速度影響整個系統的性能。

5 現場更新

當設備用于現場時,提供FPGA配置更新的能力就益發重要,如圖3所示。這種能力為設備供應者提供了競爭優勢,能對標準的改變、新的服務以及排除故障作出迅速回應。

圖3 在現場更新邏輯

LatticeXP2器件

LatTIce與富士通(Fujitsu)合作開發了90nm嵌入式閃存工藝的 LatTIceXP2系列,這種工藝使LatTIceXP2器件的成本減少了50%。該器件把成功用于LatTIceECP2 SRAM的功能塊和Flash單元組合在一起,稱之為flexiFLASH。

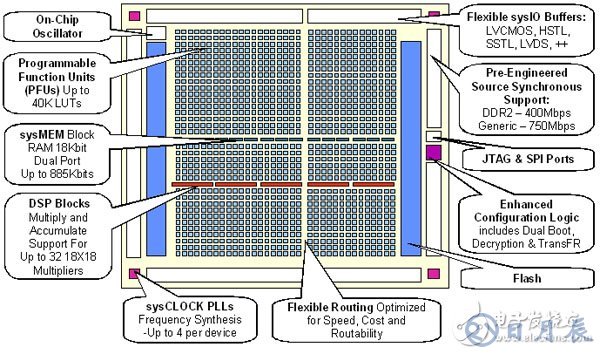

1 LatticeXP2結構-功能塊

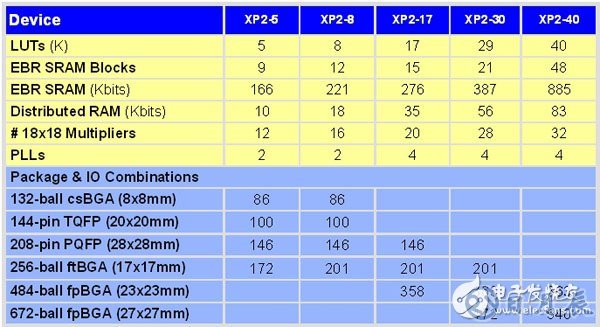

LatticeXP2器件的核心含有能夠實現邏輯的可編程功能單元(PFU),以及占25%邏輯塊的分布式存儲器。用4輸入的查找表和寄存器對來實現邏輯,對于FPGA工業、能夠被系統設計者充分理解以及邏輯綜合工具提供者來說,這是一個事實上的標準。分布式存儲器為設計者提供了有效的方法實現便箋式存儲器。這個系列提供5K到40K LUT。

嵌入式RAM(EBR)的sysMEM行提供166K -885Kb的18kb塊的雙口存儲器。器件還有乘、加、減和累加功能的sysDSP塊,用來實現通用的DSP功能,例如FIR濾波器、FFT和復雜算法。sysDSP塊提供12-32的18x18乘法器。

器件的I/O引腳數從86到540,能與各種I/O標準互連,包括LVCMOS、PCI、LVTTL、LVDS和SSTL, HSTL。此外與附加的外部電阻相配合可以模仿LVPECL、BLVDS 和RSDS接口標準。校準DQS延時塊的DLL、DDR寄存器和時鐘傳送電路能實現達400Mbps的DDR和DDR2存儲器接口。還可以與器件一起實現750Mbps的普通DDR接口。

器件還提供多達4個PLL,用于時鐘綜合與對齊。片上振蕩器提供低精度的時鐘源,適用于許多輔助功能,例如監視時鐘和鍵盤掃描邏輯。時鐘的分布為8個全局時鐘、8個區域時鐘,或者2個高速邊沿時鐘。圖的左邊和右邊為Flash存儲器塊,用于器件的配置。

器件工作于1.2伏的內部電壓并有各種可供選擇的封裝。圖4為器件的整個結構,圖5為系列中的各個成員的詳情。下面將詳述非易失特性的運作。

圖4 LatticeXP2結構

圖5 flexiFLASH結構

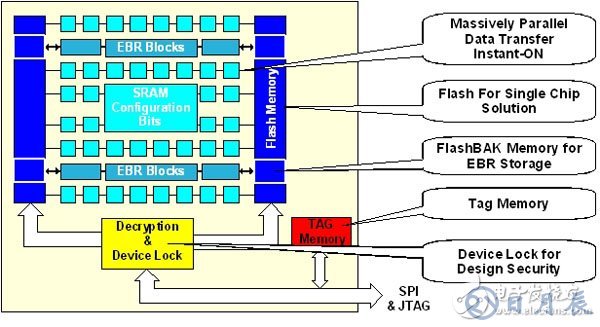

FlexiFLASH詳情

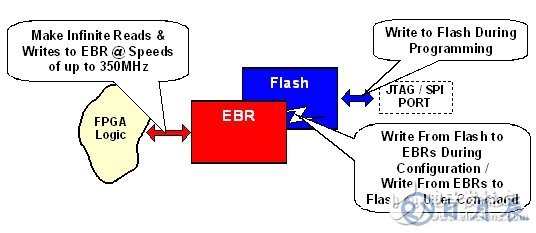

LatticeXP2器件在結構中組合了Flash 和SRAM,稱為flexiFLASH。器件邏輯配置和嵌入式RAM塊數據存儲在SRAM單元。上電時或者根據用戶命令,源于片上Flash存儲器的塊以并行形式載入SRAM。這種迅速的傳送方式使器件具有瞬時的特性,片上的Flash存儲器導致了單片解決方案。通過JTAG 或者SPI端口可以對Flash存儲器進行寫操作,如圖5所示。

FlashBAK存儲器

為了滿足存儲大塊的數據,LatticeXP2器件提供稱為FlashBAK存儲器的創新功能。如前所述,上電時從片上Flash存儲器裝載至EBR。EBR能以350MHz的速度進行讀或寫。可以根據要求在FPGA內切換信號,根據當前EBR的內容,重寫Flash是可能的。這個過程大約為1秒的時間。用這個方法,用戶可獲得高性能和無限次的讀和寫,這是非易失Flash存儲器與SRAM相結合的結果。這個器件提供166K 和 885Kbit的 FlashBAK存儲器。

圖6 非易失FlashBAK存儲

串行TAG存儲器

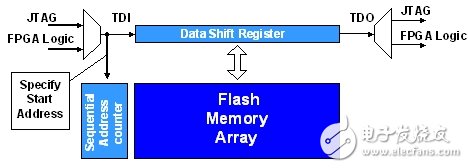

為了提供小量可串行訪問的存儲器,每個器件都有0.6K至3.4Kbit的串行TAG存儲器。如圖7所示,可以通過器件的JTAG接口或者FPGA邏輯訪問這個存儲器。這個存儲器位于器件安全結構的外面,可以獨立地訪問器件安全設置。

圖7 串行TAG存儲器

器件鎖提供設計安全

如前所述,許多設計者都要確保設計安全地鎖定在FPGA之內。用物理的方法來檢查FPGA 的SRAM單元幾乎是不可能的,因為SRAM單元掩埋在多層金屬下。防止通過JTAG 或者SPI端口查詢器件配置的保密位進一步完善了安全性。

為了防止未授權的篡改,器件有64位的碼,一旦設置后,在擦除或者重寫Flash時需要驗證。對于客戶要求更加安全的解決方案,還有一次性編程(OTP)的模式。一旦器件處于這種模式,就不能擦除或者對器件再編程。

全面的現場更新

如前所述,實現現場更新的設計者要求最大的設備正常運行時間、很好的可靠性和高的安全性。為了滿足這些要求,LatticeXP2器件提供TransFR I/O、雙引導和128位AES解密。

針對最大正常工作時間的TransFR I/O

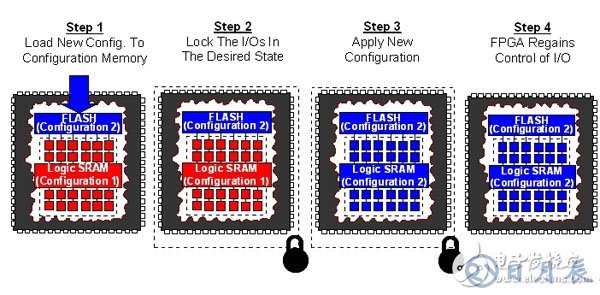

在系統配置期間,大多數FPGA的I/O均為三態。這種缺少控制的狀態通常迫使循環上電以便更新FPGA的配置。如同其他的Lattice FPGA,LatticeXP2器件具有TransFR I/O,在器件配置期間能凍結I/O的狀態。這樣現場更新的器件就有最小的中斷和停機時間,系統設計者能夠滿足高系統正常運行時間和現場更新邏輯的雙重要求。圖8展示了TransFR I/O更新的4個步驟。因為新的配置可以在后臺載入LatticeXP2的片上Flash,新的配置載入SRAM是很快的。鎖定I/O,施加新的配置,再釋放I/O的時間小于2毫秒。

圖8 TransFR I/O更新的4個步驟

針對可靠性的雙引導方案

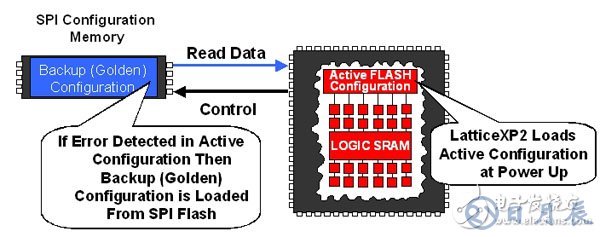

存儲的FPGA配置被更新時,存在著電源或者通信失敗的風險,會導致不可靠的配置和系統停止工作。如果發生了這種情況,拜訪技術員和糾正差錯都是不小的開支。為了防止發生此類問題,LatticeXP2器件可以使用外部的SPI存儲器來實現雙引導方案。

如圖9所示,上電時LatticeXP2試圖從片上Flash載入SRAM配置位。如果在這個過程中檢測到錯誤,于是FPGA從外部的SPI存儲器讀取備份或者重要的配置。用這種方法運行系統,能夠可靠地進行更新而不管電源或者通信故障。

圖9 高可靠現場更新的雙引導方法

用于設計安全的128位加密

LatticeXP2器件能用可選的128位AES編程數據加密。器件收到加密數據時,用片上的解密引擎進行解密,解密引擎是用戶定義的用Flash存儲器存儲在片上的密鑰。基本的操作如圖10所示。這種運作模式使得在現場更新期間敏感的設計數據得到了保護。

本文小結

設計者選擇非易失器件的主要原因仍然未變,這些原因是小的尺寸、瞬時以及高可靠性。然而對非易失數據存儲和全面的現場更新解決方案的新要求正在興起。所有這些新要求都必須滿足,而且,相對于傳統的SRAM解決方案,非易失解決方案的額外費用是最小的。

如今有兩種方法提供非易失FPGA:混合的和單片的。混合方法主要是解決小尺寸的要求。而真正的單片非易失方法滿足了小尺寸、瞬時和高安全性的要求。

采用90納米嵌入式Flash工藝,LatticeXP2 FPGA滿足了選擇非易失器件的主要和新興的原因,同時還降低了成本。

表1 LatticeXP2 FPGA 系列

作者: 萊迪思半導體公司