CCD是一種廣泛應用于成像系統中的光學傳感器,TDI-CCD利用延時積分的方法,通過對同一物體多次曝光,實現增強型光能采集的目的。同時,根據像移補償的速度,設計TDI-CCD的電荷轉移速率,能夠實現電子學像移補償。本文闡述的成像系統以TDI-CCD為核心,利用FPGA實現CCD圖像數據整合功能的硬件系統。由于FPGA在資源、速度、效率、穩定性等方面有很多優勢,因此,采用FPGA實現高速、大規模、繼承性好的成像軟件,通過在軟件結構、模塊和設計方法上的優化,尋求更加合理設計方案,達到功能和性能的提升。本文將FPGA設計的一些指導性原則應用于實際的系統設計中,給出了FPGA自頂向下的軟件結構劃分,以及程序設計中的注意事項。通過對模塊接口信號的解耦處理,增強了系統的適應性和穩定性,該軟件系統在實際工程中已進行驗證。

1 成像系統結構

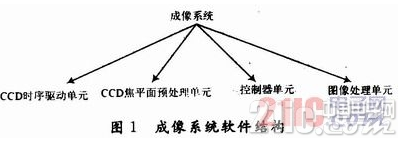

成像系統以TDI-CCD為核心,采用FPGA作為核心數據處理單元,實現數據處理傳輸,其基本組成部分如圖1所示。

時序驅動單元采用FPGA產生驅動時序,通過硬件電路實現對CCD控制信號驅動;焦平面單元將CCD視頻信號經過預放、濾波、相關雙采樣(CDS)、A/D轉換后輸入到圖像處理單元;圖像處理單元接收控制器指令,完成總體對成像系統的控制,以及圖像數據的整合傳輸等功能;

2 成像軟件設計

成像系統軟件采用FPGA實現。軟件核心是圖像處理單元。該單元接收CCD行同步信號以及指令,完成數據處理功能;

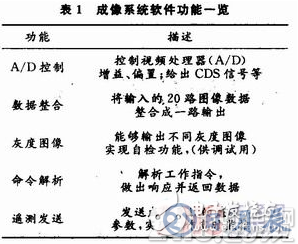

成像系統FPGA的主要功能如表1所示。成像系統在物理上分為3個電箱。圖像處理電箱獨立存在,并接收焦平面電箱的視頻信號和控制電箱工作指令,實現數據處理。根據系統邏輯功能劃分FPGA軟件結構,并將軟件設計規范應用其中,優化系統性能。圖像處理單元工作頻率高,數據處理復雜,不同的結構劃分和設計方式對性能影響較大,因此,本文對圖像處理軟件設計進行詳細闡述。

2.1 FPGA軟件設計分析

可編程邏輯設計原則的合理應用,為理解FPGA程序設計,實現高效、穩定的數字系統提供了條件。

(1)資源與速率的平衡。資源和速率是FPGA設計的重要指標。通過合理的軟件結構劃分,在高速數據處理區域采用速度優先方法,即通過模塊復用、串/并轉換、數據流水化等方法實現高速數據傳輸;在低速處理區域,采用串行方式和組合邏輯,通過增加扇出實現資源的最優化。

(2)系統與硬件匹配。FPGA內部硬件資源決定設計的結構和方法。采用BLOCK RAM或Distributed RAM,根據數據處理內容、資源利用率要求決定使用方式;另外,利用全局信號線,實現全局變量處理;利用FPGA內部IP和原語實現程序設計,改善程序架構。

(3)同步設計。同步設計是資源與速度的體現,在異步時鐘域數據處理時,采用FIFO轉存,解決同頻異相或異頻問題,實現數據讀取和傳輸。

(4)可靠性設計。軟件設計采用冗余和容錯性設計、簡化設計規模和減少軟件配置項;

2.2 圖像數據處理與分析

2.2.1 數據率和時鐘選擇

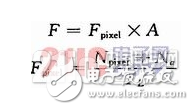

CCD圖像輸出數據率計算如下:

式中:F為輸出數據率;Fpixel為CCD像元轉移速率;A為量化等級;Npixel為像元數;Na為啞像元數;TL為行周期。根據指標計算,成像系統的數據率達到1 Gb/s以上,因此,數據傳輸采用10 b數據并行方式,滿足軟硬件設計預定的指標要求。

2.2.2 時鐘域分析

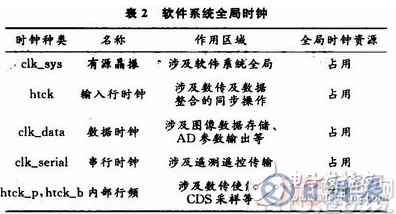

CCD圖像處理單元,主時鐘采用120 MHz有源晶振(elk_sys),通過FPGA內部全局時鐘網絡(BUFG)實現全局走線;設計時不建議使用DCM。系統的主要時鐘如表2所示。

系統接收外部行同步時鐘,通過高頻主時鐘同步,并在FPGA內產生內部行頻,用于產生CDS信號及控制邏輯。通過分頻產生串行時鐘,完成遙控遙測信號的收發;產生數據時鐘,完成數據采樣和傳輸;

2.2.3 成像系統軟件結構及功能實現

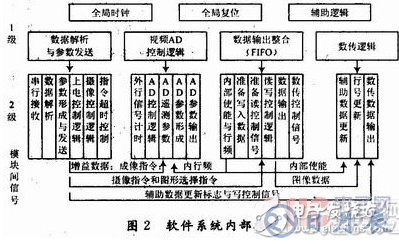

根據軟件系統功能,自頂向下劃分模塊,如圖2所示。為了保證模塊間信號的獨立性,增強了模塊解耦處理,具體的處理原則是:減少模塊IO數量,減少邏輯關聯程度,避免信號控制環路產生;存儲器與后續數據處理操作整合;模塊間避免數據傳輸,減少異步時鐘域的數據同步問題;采用脈沖電平邏輯實現模塊控制等。由于合理劃分了軟件模塊,方便了模塊化設計和仿真驗證,為后續的工作奠定了堅實的基礎。圖2中三級模塊沒有具體給出。

(1)數據解析模塊。通過RS 422解析串行指令,同時完成部分硬指令翻譯,并根據指令要求發送系統遙測參數。串行接收數據采用累加校驗,并對接收數據進行預存儲。校驗正確后,將數據以乒乓方式存入RAM,以保證讀/寫邏輯不沖突;校驗錯誤時,不轉存數據。根據不同的指令類型,對相應的地址進行讀/寫操作,更新完畢后給出標志位。

(2)視頻控制模塊。輸出A/D參數、CDS信號和A/D輸出時鐘。A/D參數采用廣播方式,通過使能信號完成20路AD的配置;由外行信號htck同步A/D的控制邏輯以及CDS信號;由于數據處理速度較低,實現時,通過增加扇出、減少模塊復用,來降低資源利用率。CDS采樣脈沖的位置對信號質量影響很大,需要精細調節。在設計時,采用FPGA內部移位寄存器生成不同位置的采樣脈沖,在調試中實現精確對準。

(3)數據整合模塊。將輸入的20路圖像數據整合一路輸出。根據工作指令選擇灰度圖像或實時圖像,并行存儲到相應的fifo中;輸出時,通過控制讀使能信號,實現數據的循環讀取。設計FIFO時,仍然采用乒乓方式,通過標志信號使讀寫邏輯分離。相比RAM設計而言,避免了大規模地址線造成的亞穩態問題,設計時序相對簡單。

(4)數據輸出模塊。根據衛星指令將圖像數據按照規定格式輸出。設計時,需要注意數傳協議中各數據段數據的輸出時序。因此,良好的模塊規劃,更有利于程序的實現和驗證。

2.3 性能與設計要點

(1)FPGA內部時鐘域分析有利于同步設計的實現,在良好的時鐘分配下,能夠提高系統運行頻率,增加軟件可靠性。根據FPGA資源說明,每個slice有固定數量的觸發器和查找表(LUT)資源,合理利用可以降低器件資源的利用率。

(2)組合邏輯容易產生亞穩態,為系統帶來不確定因素,同時,組合邏輯延時也限制了系統的運行頻率。在頻率要求較高的模塊內部,可以采用流水線技術降低組合邏輯規模。

(3)軟件結構對系統性能和資源使用有很大的影響;不合理的結構劃分不僅浪費資源,也不利于軟件的升級和維護。該軟件通過合理的結構和接口信號劃分,力求達到模塊解耦的目的。通過詳細的接口時序說明,可以更好的進行軟件維護和更新,為后續開發奠定基礎。

2.4 關于軟件系統工作頻率和硬件速度的匹配

電路設計時,通過分析硬件電路的芯片參數和電路延時指導軟件設計。對于關鍵信號走線,除了可以在硬件上設置延時線外,FPGA內部可以通過DLL倍頻時鐘,通過時鐘計數方式實現延時,或者通過FPGA內部LUT和門邏輯實現組合邏輯延時設計。由于FPGA的端口速率有限,不同等級的FPGA芯片的處理速度也不同,因此,需要參考FPGA的參數特性設計系統結構,并確定端口數傳規則和內部結構,同時,注意與外圍

硬件的匹配,以保證軟硬件可靠運行。

3 實時圖像效果評估

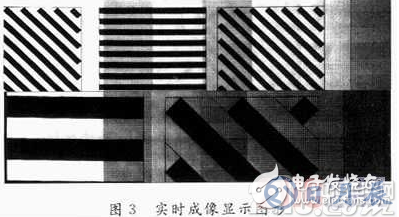

圖3給出了實驗室條件下的原始數據圖像。通過調整信號處理器的增益,調整相應抽頭的灰度值,從而達到灰度均衡效果;通過觀察相應的圖像數據可以得出,數據處理和成像效果達到預定指標要求。

4 結語

FPGA成像軟件是系統可靠運行的重要保障,其性能對整體分辨率的提高有著舉足輕重的作用。在給定的硬件條件下,通過高效設計FPGA軟件,能夠顯著提高系統性能。在成像軟件的數據處理方法上,仍然有很多方向,如實時圖像壓縮傳感,提高系統的傳輸能力;在FPGA內部進行海量數據處理等。通過實驗證明,該軟件的實際運行速度達到要求。因為硬件處理速度的限制,若想提高軟件運行頻率,尋求更加合理的軟件系統結構以及電子學分系統結構將成為重要的研究內容。