1 引言

隨著信息技術(shù)和網(wǎng)絡(luò)化進(jìn)程的發(fā)展,網(wǎng)絡(luò)通信安全問題日益突出。現(xiàn)場可編程門陣列(FPGA)以其自身設(shè)計(jì)靈活、可靠性高的優(yōu)點(diǎn)廣泛應(yīng)用于加密領(lǐng)域。硬件實(shí)現(xiàn)的加密算法不占用計(jì)算機(jī)資源.加密過程完全與外部總線隔離,具有較高的數(shù)據(jù)保護(hù)能力。算法可靈活改變,具有較強(qiáng)的獨(dú)立性。加密機(jī)由單片機(jī),F(xiàn)PGA和El通信接口組成。FPGA內(nèi)部算法由VHDL語言編寫。該系統(tǒng)適用于要求數(shù)據(jù)安全較高的場合,其終端可為計(jì)算機(jī),銀行POS機(jī)等,提供數(shù)據(jù)傳輸?shù)陌踩院捅C苄浴?/p>

2 流加密解密原理及算法

2.1 流加密解密原理

流密碼由密鑰和密碼算法兩部分組成,密鑰一般存儲在加解密設(shè)備內(nèi)部,在數(shù)據(jù)傳輸前已設(shè)置完成。密碼算法在較長時間內(nèi)是不變的。在同步流密碼中,只要發(fā)送端和接收端有相同的密鑰和內(nèi)部狀態(tài),就能產(chǎn)生相同的密鑰流。

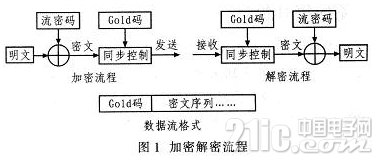

數(shù)據(jù)傳輸時,加密端和解密端使用同一個初始密鑰,加密時密碼流與明文相異或得到密文,同時每隔一定時間加入同步數(shù)據(jù);解密時以同步模式產(chǎn)生的密文與密碼流進(jìn)行異或得到明文,同步模式采用63位Gold碼。整個加解密過程與發(fā)送數(shù)據(jù)格式如圖1所示。在發(fā)送密文中加入初始同步碼,接收端利用Gold碼的三值特性檢測Gold碼實(shí)現(xiàn)同步數(shù)據(jù)。對接收數(shù)據(jù)流和Gold碼做互相關(guān)運(yùn)算,相關(guān)結(jié)果滿足Gold碼的三值特性,說明當(dāng)前數(shù)據(jù)流是發(fā)送端加入的同步Gold碼.標(biāo)志為密文的起始,然后調(diào)用解密算法對后續(xù)的密文解密,恢復(fù)傳輸?shù)臄?shù)據(jù)。

2.2 A5/1算法原理

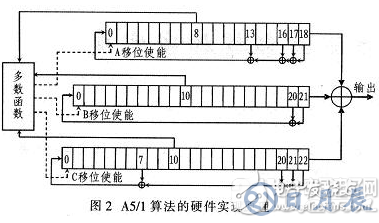

A5/1引是GSM移動通信中數(shù)據(jù)傳輸?shù)牧髅艽a加密算法。A5/1密碼流產(chǎn)生器生成的密碼與明文數(shù)據(jù)幀的每一位相異或得到密文序列。A5/1算法由3個不同長度的線性反饋移位寄存器R1,R2,R3組成,其長度分別為19,22,23位,其反饋特征方程分別為:x18+x17+x16+x13+1,x22+x21+x20+x7+1。算法的初始密鑰是64位向量。密碼流輸出位為3個移位寄存器的異或輸出。移位寄存器的使能由多數(shù)函數(shù)控制。Rl的第8位、R2的第10位、R3的第10位為多數(shù)函數(shù)數(shù)據(jù)輸入,它們決定3個移位寄存器的移位狀況。在這3個數(shù)據(jù)位中,如果有兩個或兩個以上的都為0,多數(shù)函數(shù)值就為0;如果有兩個或兩個以上的都為1,多數(shù)函數(shù)值就為1。多數(shù)函數(shù)輸入的3個數(shù)據(jù)位中與多數(shù)函數(shù)值相同,相應(yīng)的移位寄存器就移位。A5/1的硬件實(shí)現(xiàn)原理如圖2所示。密碼流的產(chǎn)生分兩個階段.第一階段給寄存器裝人64位初始值;第二階段則根據(jù)時鐘節(jié)拍和使能控制產(chǎn)生密碼流。

2.3 W7算法原理

W7H算法與A5/1算法在結(jié)構(gòu)原理上有相似之處。W7算法由8個類似于A5/1算法硬件結(jié)構(gòu)模塊并行組成,每一個模塊都包含3個線性反饋移位寄存器和多數(shù)函數(shù)。不同的是w7算法是128位的初始密鑰,線性反饋移位寄存器的長度圖2 A5/1算法的硬件實(shí)現(xiàn)原理和反饋結(jié)構(gòu)都不同于A5/1算法。3個線性反饋移位寄存器長度分別為38、43、47位。8個并行模塊采用同一初始密鑰。但反饋結(jié)構(gòu)和多數(shù)函數(shù)的輸入位均各不相同。8個模塊的輸出組成8位密碼流,加密效率更高。各線性移位寄存器由固定數(shù)據(jù)位通過邏輯與產(chǎn)生1位數(shù)據(jù),再將該位數(shù)據(jù)與最高位輸出異或,最后將3個移位寄存器輸出再異或輸出作為本并行塊的密碼位輸出。由于有8個并行塊,最后總的輸出8 bit,即1字節(jié)。設(shè)計(jì)時,每隔8個時鐘周期輸出一次,保證數(shù)據(jù)速率的一致性。

3 系統(tǒng)硬件設(shè)計(jì)

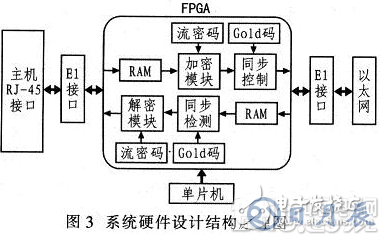

該系統(tǒng)硬件設(shè)計(jì)由單片機(jī),F(xiàn)PGA和El接121等組成,如圖3所示。單片機(jī)用于輸入用戶初始密鑰;FPGA負(fù)責(zé)密鑰流產(chǎn)生以及加解密;E1接口實(shí)現(xiàn)數(shù)據(jù)流的發(fā)送和接收,完成HDB3碼和TTL電平之間的轉(zhuǎn)換,實(shí)現(xiàn)通信接口單元和協(xié)議數(shù)據(jù)處理單元之間的全雙工通信。

由于通信鏈路采用E1標(biāo)準(zhǔn),該系統(tǒng)設(shè)計(jì)的外部數(shù)據(jù)鏈路接121采用E1接口,選用接口器件DS21348。DS21348支持El和T1線接口單元,通過寄存器設(shè)置選擇E1線接口單元。DS21348可配置為硬件模式,完成HDB3到TTL、TTL到HDB3的電平轉(zhuǎn)換,時鐘同步、數(shù)據(jù)信號格式轉(zhuǎn)換以及數(shù)據(jù)幀處理。該系統(tǒng)可并行處理兩路數(shù)據(jù),一路加密,一路解密,實(shí)現(xiàn)全雙工通信。

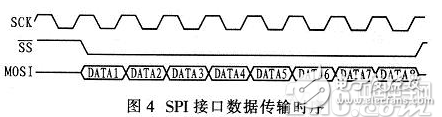

由于TI公司的MSP430系列微處理器平臺具有低功耗和小體積等特點(diǎn),適合便攜式應(yīng)用場合,所以單片機(jī)采用MSP430系列,并通過SPI接口實(shí)現(xiàn)與FPGA的數(shù)據(jù)通信。單片機(jī)外接一鍵盤,用于輸入初始密鑰。考慮到用戶輸入密鑰位數(shù)不能很多,可設(shè)置簡短的密鑰,并在單片機(jī)內(nèi)部擴(kuò)展至算法所需的位數(shù),然后通過單片機(jī)SPI接口傳送至FGPA。SPI接口共4條信號線:串行時鐘(SCK),主機(jī)輸出/從機(jī)輸入(MOSI),主機(jī)輸入/從機(jī)輸出(MISO),從機(jī)片選(SS)。SPI接口可配置為主或從模式。設(shè)計(jì)配置為主模式。當(dāng)單片機(jī)向FPGA傳輸命令或數(shù)據(jù)時,應(yīng)用SPIO模式。當(dāng)片選信號丙拉低,在每個時鐘(SCK)的上升沿發(fā)送數(shù)據(jù),無需FPGA向單片機(jī)輸人數(shù)據(jù),所以不使用MISO數(shù)據(jù)線。片選信號SS與FP-CA的RAM的使能相連,控制數(shù)據(jù)讀入。當(dāng)用戶輸人初始密鑰后,經(jīng)過數(shù)據(jù)擴(kuò)展,與算法選擇數(shù)據(jù)通過SPI接口傳送至FPGA。SPI接口時序如圖4所示。

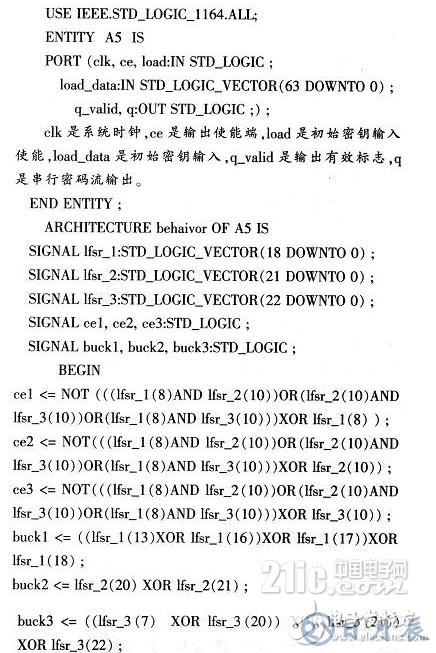

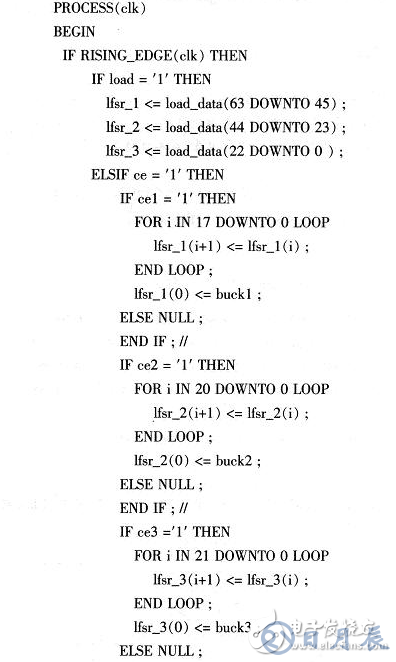

FPGA采用CyeloneII系列中的EP20F256C6,該器件是低成本架構(gòu)FPGA,可提供多達(dá)18 752個邏輯單元.152個用戶IO,239 616 bit的存儲位,密度超過CyeloneI FPGA的3倍,完全滿足系統(tǒng)設(shè)計(jì)需要。CycloneII FPGA內(nèi)部的邏輯資源可實(shí)現(xiàn)復(fù)雜應(yīng)用。CyeloneII器件采用的低成本串行配置器件,這種串行配置器件最大可提供64 Mbit的nash存儲器。所以,采用EP20F256C6可高效完成系統(tǒng)核心算法,有效節(jié)約成本。其內(nèi)部算法由VHDL語言編程實(shí)現(xiàn)。主要程序模塊:加解密算法模塊(A5/1和W7)、數(shù)據(jù)存儲模塊、同步產(chǎn)生模塊、同步檢測模塊。加密和解密各有一套獨(dú)立的模塊集合。其中A5/1算法模塊的VHDL代碼如下:

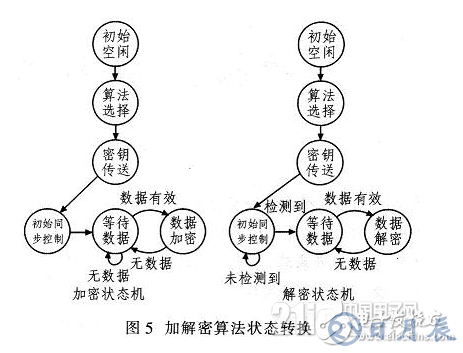

FPGA的模塊控制由兩個獨(dú)立的狀態(tài)機(jī)組成,用于處理加密算法和解密算法,其狀態(tài)轉(zhuǎn)換如圖5所示。

系統(tǒng)上電初始化后,由用戶向單片機(jī)輸入初始密鑰和算法選擇數(shù)據(jù),通過SPI接口送入FPGA,F(xiàn)PGA接收到密鑰后將初始密鑰傳給算法模塊,算法模塊初始化后產(chǎn)生同步Gold碼,并等待數(shù)據(jù),當(dāng)待加密數(shù)據(jù)有效時,啟動加密算法;當(dāng)數(shù)據(jù)無效時,再次進(jìn)入等待數(shù)據(jù)狀態(tài)。相應(yīng)地,解密模塊先檢測起始的同步Gold碼,檢測到后,當(dāng)待解密數(shù)據(jù)有效時,啟動解密算法,當(dāng)待解密數(shù)據(jù)無效時,再次進(jìn)入等待數(shù)據(jù)狀態(tài)。如此往復(fù),完成數(shù)據(jù)的加密解密過程。在密鑰傳輸過程中,由于兩種算法所需的初始密鑰位數(shù)不同,當(dāng)使用w7算法時,初始密鑰在送入FPGA中后還需二次擴(kuò)展達(dá)到所需的位數(shù)。

4 仿真與分析

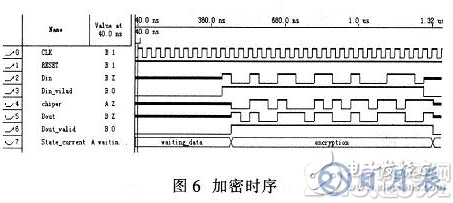

采用QuartuslI 8.0軟件仿真FPGA功能。共用4 865個邏輯單元,1 024 bit的片上存儲位,時序分析得到最大工作頻率為95.79 MHz。仿真加密時序如圖6所示。

5 結(jié)論

通過對整個設(shè)計(jì)的調(diào)試驗(yàn)證,結(jié)果滿足設(shè)計(jì)要求。整個系統(tǒng)具有較高的安全性和保密性,可為要求通信安全的網(wǎng)絡(luò)應(yīng)用提供一種基于硬件的加密方式,基于FPGA的加密算法設(shè)計(jì)具有很高的靈活性,如果采用更加先進(jìn)的加密算法,可進(jìn)一步提高系統(tǒng)的安全性和保密性。