功率放大器是構建新一代通信系統的核心組件,這類通信系統需要超寬的帶寬以支持高數據速率。為了設計一款高效的功率放大器,晶體管必須工作于開關模式之下,并且/或者具有反射端接諧波。然而,為了能在一個以上倍頻程帶寬下正常工作,在較低頻率下,諧波端應在帶內。此外,Bode-Fano帶寬理論認為,對于給定的復合負載,可實現帶寬存在一個基本限值,該限值會降低目標負載阻抗,進一步偏離高效條件。

在本文中,我們將比較和對比兩種不同的寬帶高效功率放大器設計技術。一種設計采用一種非均勻分布式放大器拓撲結構,完全集成于一個MMIC之中,其輸入和輸出匹配至50 Ω。另一種設計采用混合式設計技術,在封裝中集成了橋接-T輸入匹配MMIC。本文將首先簡要描述電路制造工藝,然后逐一展示和討論各種設計拓撲結構。

器件技術和工藝

這里使用的AlGaN/GaN HEMT器件基于TriQuint的0.25 μmGaN工藝TQGaN25,采用100mm SiC晶圓制成。這是一種TriQuint推出的大規模制造技術。在PAE匹配條件下,一個四指100μm柵極寬度晶體管(偏置電壓:Vd=40V,Id=100 mA/mm)的典型功率密度為5.5W/mm,10GHz時的PAE為60%。

分布式放大器設計

A. 電路設計

為了實現最高的功率和效率,我們選擇了非均勻分布式功率放大器(NDPA)拓撲結構。NDPA不是以50Ω的阻抗端接漏極線路,而是采用了漸變傳輸線。為每條傳輸線路選擇特定的寬度,以便為每個單元提供最佳負載。在某些情況下,各個單元的器件尺寸也采用漸變設計。

由于目標工作頻率為30MHz至2.7GHz,所以,我們選擇了5-單元設計,器件總周長為2.4mm,以實現功率、增益、帶寬和芯片尺寸的平衡。隨后,我們計算出了各單元的器件尺寸和傳輸線路阻抗。結果如表1所示。第一個單元的尺寸為1.2mm,其目的是實現功率和效率的最大化。其余單元尺寸相等,均為0.3mm。請注意,在表1中,有一列為各個單元的漏電流(Id)。該電流表示器件的最大驅動電流,設定了輸出走線的最小寬度。

MMIC成品如圖1所示。芯片的最終尺寸為2.4mm×1.8mm。為了支持最低30MHz的工作頻率,我們選擇了片外偏置選項。這種設計的一個特點是在第一單元輸出端使用了線圈。請參考前面的表1,處理450mA電流所需的最小寬度為30μm。然而,在100μm厚的SiC基板上,寬30μm線路的典型阻抗只有76Ω,離最佳負載100Ω還有很大的差距。然而,線圈實際上會通過互耦合的方式增大線路的有效阻抗,仿真條件下,該線路的阻抗為105Ω。這樣就可以實現高效運行。

B. MMIC測量值

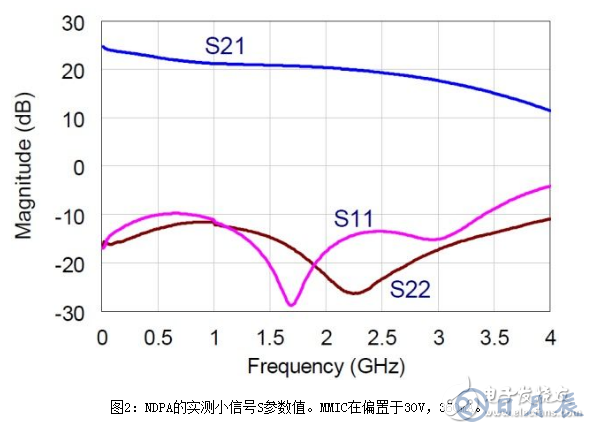

我們把MMIC成品焊接在一塊厚40密耳的CuMo承板上,同時把RO4003板裝在MMIC周圍,以便進行評估。我們對電路板上的50?走線進行了去嵌入處理,使測量參考平面位于焊線的末端。如圖2所示,在30MHz至2.7GHz范圍內,典型增益為20dB,并且在相同頻率范圍內,輸入和輸出回波損耗為10dB或更低。

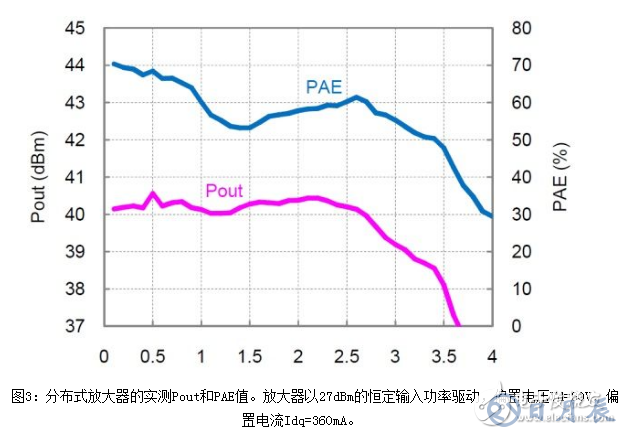

大信號測量值表明,結果良好。圖3所示為MMIC在整個頻率范圍內,在27dBm的恒定輸入功率(這相當于約5dB的壓縮值)下的輸出功率和PAE。當漏極電壓為30V時,MMIC在不超過2.5GHz的整個頻率范圍內可產生大于10W的輸出功率,在不超過2.7GHz的范圍內,可產生8W或以上的輸出功率(功率密度超過4 W/mm),并且在整個頻段,PAE均優于52%。在500MHz以下,MMIC可實現近70%的PAE。如此高的PAE源于第一個單元加載了高阻抗。請注意,這里展示的功率和PAE測量值只是在基頻輸出功率條件下得到的結果,不得用于計算功耗。要計算功耗,我們必須使用總功率,包括諧波下的所有功率。

混合分立式功率放大器設計

電路設計

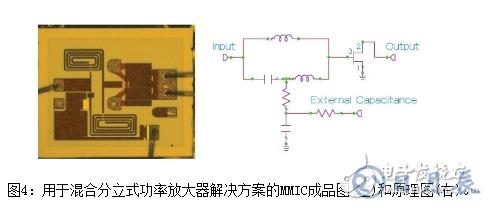

我們前面展示的分布式放大器技術對MMIC效果明顯。然而,對于混合分立式設計來說,要實現多級是十分困難的。我們選擇采用一種橋接T拓撲結構,將單個晶體管的輸入端匹配至50Ω。我們選擇了合適的晶體管的尺寸,以便輸出端的50Ω端口與其目標負載線完好匹配,因此,放大器輸出端可以不匹配。我們選擇了一款周長為1.24mm的晶體管。另外,借助周長為2.48mm的晶體管也可實現不錯的負載線,其一般具有更高的效率和更低的功率密度。要進一步優化性能,可以在電路板級進行更多匹配。MMIC成品如圖4所示。芯片的最終尺寸為1.277mm ×1.06mm。用周長為2.48mm的晶體管(本文中未討論)打造的另一款芯片的尺寸為1.277mm ×1.305mm(大23%)。

橋接T拓撲結構是Zobel網絡的修改版,可以在輸入端提供恒定阻抗。用于匹配晶體管輸入端的拓撲結構如圖4所示。該電路的匹配設計可在30MHz至2700MHz范圍內提供良好的回波損耗性能。橋接T匹配的不足之處在于,網絡損耗較大。然而,在這些低頻下,晶體管擁有較大的增益,可以平衡掉這些損耗,從而使芯片在各種頻率下均能無條件保持穩定。因此,對于該工作頻率,橋接T是一種非常合適的選擇,不會影響性能。

橋接T網絡的低頻性能在很大程度上取決于并聯網絡中的阻抗。為了在低頻下實現實部阻抗,需要使用一個較大的電容。為此,我們用一個焊盤連接一個片外電容(見圖4中的外部電容)。由于MMIC的輸入端已匹配至50 Ω,因此,輸入網絡不需要進行其他匹配。此外,器件在尺寸設計上已在輸出端提供近50 Ω的負載線,因此,輸出匹配網絡只需要一個串聯L并聯C網絡以保障高頻性能,然后,在低頻下提供50Ω的負載阻抗以保障寬帶性能。輸入和輸出匹配網絡都采用了寬帶偏置網絡,并部署在一塊4“×3”的應用板上。

混合式放大器的測量值

我們在一塊用Rogers 4350B制成的電路板上對最終器件進行了測試。50Ω匹配輸入表現良好,能在40MHz至2.7GHz的范圍內實現10dB的回波損耗,在低至30MHz的頻率范圍內實現7dB的回波損耗(圖5)。器件在低頻下實現12dB的增益,在高頻下實現17dB的增益。

在32V和脈沖條件下,放大器實現了5W的典型輸出功率(或者,4W/mm的功率密度),在1至2.7GHz范圍內實現45%的功率附加效率(圖6)。我們選擇了脈沖而非CW工作模式,因為評估板限制了總功耗。另外,我們在1至2.7GHz范圍內對數據進行了測量,因為我們無法在1GHz以下構建脈沖試驗臺。

討論

結果表明,兩款放大器均能在30~2700 MHz范圍內工作,二者具有相似的輸出功率密度。完全匹配的MMIC在器件尺寸以及輸出功率的選擇方面表現出較大的靈活性,但其代價也比較大。另一方面,我們展示的混合式解決方案具有較為獨特,器件尺寸固定,因此對性能形成了限制;較小或大得多的晶體管都無法在整個帶寬范圍內取得良好效果。但是,由于芯片尺寸非常小(為MMIC的1/4,但功率僅少一半),因此其代價更能令人接受。另外,最多可以使用兩倍周長的晶體管,可實現類似MMIC的性能,芯片尺寸增幅也不大(23%),并且混合式解決方案可使用外部元件進行調整,以在特定頻段范圍內實現更加優化的性能。然而,MMIC解決方案由于要處理的寄生電容較少,所以可以實現卓越的性能。歸根結底,如果系統側重于打造一種低成本的解決方案,并且可以犧牲一定的性能,則混合式解決方案是更合適的選擇。然而,如果系統要求以較高的代價提供特定的性能,則MMIC解決方案是更好的選擇。盡管如此,實踐表明,兩種設計技術都是寬帶條件下的有效選擇。

結論

本文介紹了兩種不同的放大器平臺,即全集成式MMIC和混合封裝式放大器,兩者均可在30 ~2700MHz范圍內實現領先的性能。其實現方法是在MMIC上運用行波技術,在混合式設計中,則是運用橋接T拓撲結構使晶體管匹配至50Ω。兩種技術各有優點,在性能和成本方面各有折衷。