以前GPIO上接的電路都是低電平觸發(fā)的那種,新畫了個板子有一個按鍵設(shè)計的是高電平觸發(fā),結(jié)果IO口設(shè)置成上拉輸入后,怎么讀都不正確,按鍵電路如圖1。無奈只能去調(diào)試一下,發(fā)現(xiàn)當設(shè)置為上拉輸入后,其ODR(GPIO輸出數(shù)據(jù)寄存器)相應(yīng)的也置為1,百思不得其解。

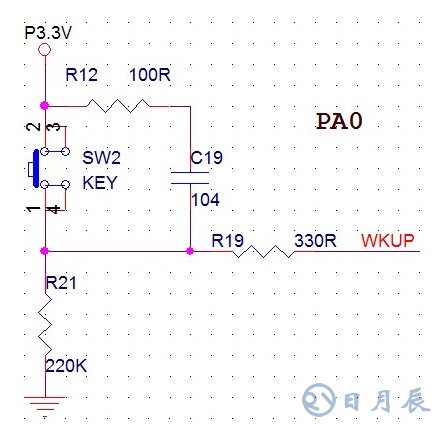

圖1 按鍵電路

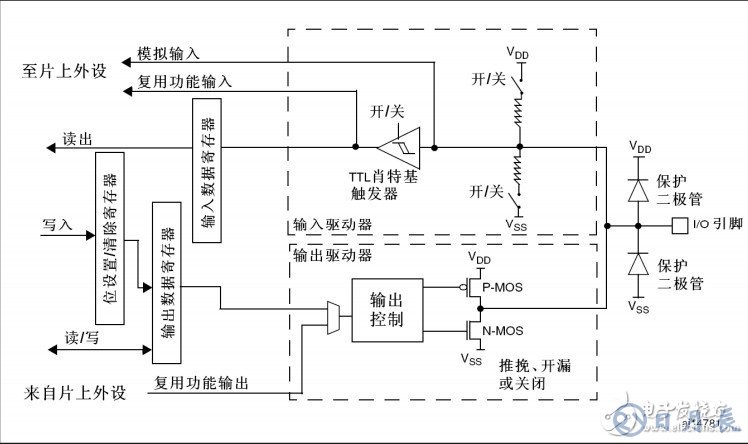

于是去看一下GPIO的結(jié)構(gòu)圖:

I/O引腳結(jié)構(gòu)圖

由圖可以發(fā)現(xiàn)其實輸出寄存器與輸入寄存器之間在I/O引腳處是線與狀態(tài),在GPIO設(shè)置成上位輸入時,其上拉電阻閉合,這時如果輸出寄存器設(shè)置為0那么在IO口內(nèi)部就會自己損耗電流,而這些電流的損耗是會增加功耗的。因此當GPIO設(shè)置成上拉輸入時,相應(yīng)的輸出寄存器也設(shè)置為1.

將按鍵電路與I/O引腳結(jié)構(gòu)圖連起來看,就清晰多了,當GPIO設(shè)置為上位輸入時,上拉電阻與按鍵的330歐、220K歐串聯(lián),這時IO口所讀到的電平就是330歐與220K歐電阻分壓的總合,由于這兩個電阻阻值過大,因引讀出的電壓大于邏輯‘1’的閥值。OK問題找到了,于是將IO設(shè)置成下拉輸入,問題就解決了。因此這里得出一個結(jié)論,IO口是上拉還是下拉要根據(jù),IO口外部接的空閑電平有關(guān),如按鍵不按下時是低電平,則應(yīng)該設(shè)置為下拉輸入。

在調(diào)試時還發(fā)現(xiàn)另一種方法可以讓代碼正常運行,就是當設(shè)置上拉輸入時,將其輸出值設(shè)置為0,這樣電平就被直接拉低了,按鍵的接地電路基本就不起作用了,但這樣做有一個壞處,前面已經(jīng)說過了,這種情況會導(dǎo)致上拉電阻直接接地了,增加了不必要功耗,而且將3.3V電壓直接加在了輸出驅(qū)動器的N-MOS上,時間長了之后可能會造成芯片損壞!