Scan(掃描測試)和BIST(內建自測試)都是用于芯片測試的技術,但它們在實現方式和應用場景上有所不同。

**Scan(掃描測試)**:

掃描測試是一種常用的數字集成電路測試技術。在設計階段,工程師會在芯片中添加額外的硬件(掃描鏈),以便在測試階段將測試數據輸入到芯片內部的特定位置,并從特定位置讀取測試結果。掃描測試主要用于生產階段的測試,以檢測出可能的制造缺陷。它可以提供很高的故障覆蓋率,但是需要外部的測試設備和復雜的測試向量生成。

**BIST(內建自測試)**:

BIST是一種將測試邏輯直接集成到被測試系統中的方法,使系統能夠進行自我測試。BIST通常包括一個測試模式生成器和一個測試響應分析器。在測試階段,測試模式生成器會自動產生測試向量,測試響應分析器會收集并分析測試結果。BIST可以在系統的生命周期中的任何時間進行測試,包括生產測試、系統啟動時的自我測試,甚至系統運行時的在線測試。BIST的優點是可以進行在系統級別的測試,無需外部的測試設備,但可能會增加設計的復雜性和硬件開銷。

Scan Design -- 掃描路徑設計

Scan 技術最初由Kobayashi等人提出來的,它的優點是基本原理是時序電路可以模型化為一個組合電路網絡。

Scan design的設計目標是能夠提高可控性和可觀測性。

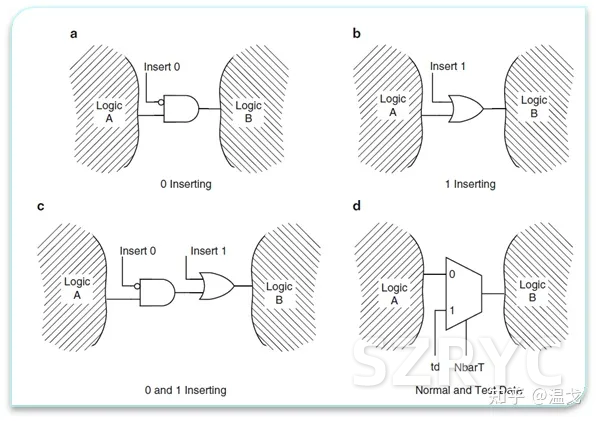

通過在邏輯A和邏輯B之間插入一些額外的硬件電路,便可觀測&控制邏輯A傳遞到邏輯B的值。[1]

scan 分為兩步:

1. Scan replacement

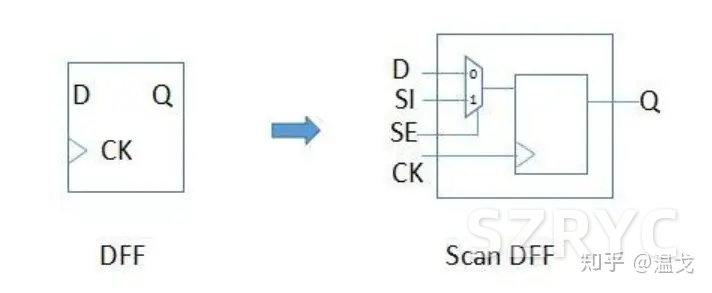

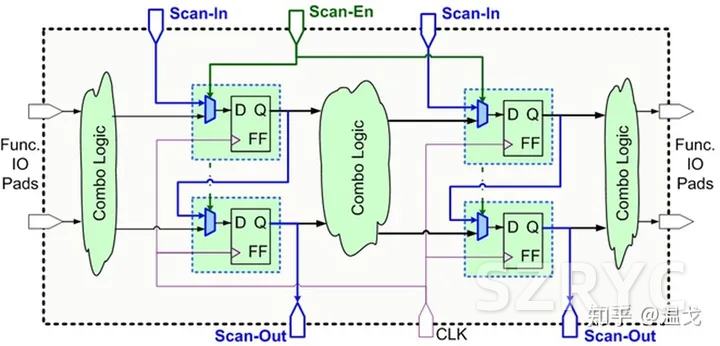

把普通的DFF,替換成帶Scan DFF,下圖是一個mux-D的DFF,可以看到多了一個SI,SE,和一個mux。

其SE端值為0時,電路工作在正常功能狀態并能把D端的值鎖存下來;當SE為1時,電路工作在所謂scan mode并鎖存SI的值。

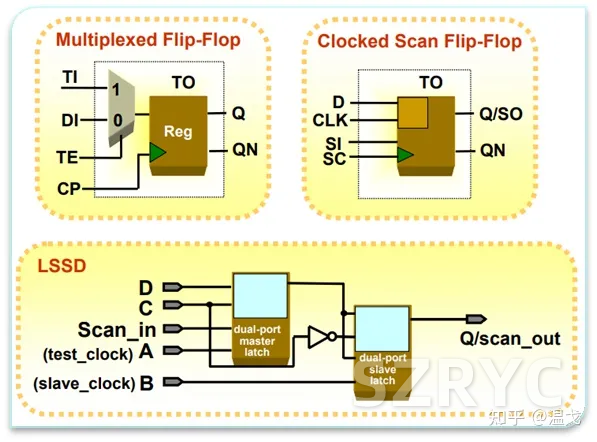

常見的scan cell有三種:

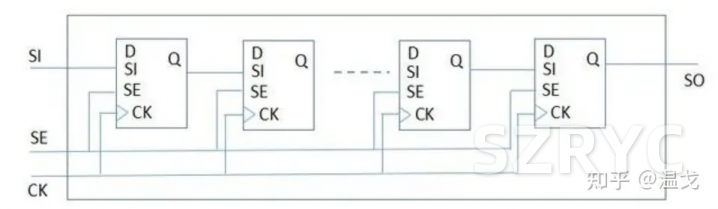

2. Scan stitching

Scan stitching 是把上一步中得到的Scan DFF的Q和SI連接在一起形成scan chain。在芯片的頂層有全局的SE信號,以及scan chain的輸入輸出信號:SI 和 SO。通過scan chain的連續動作,就可以把問題從對復雜時序電路的測試轉化成測試組合電路。

實際在設計中,這兩步都是由EDA工具完成的。

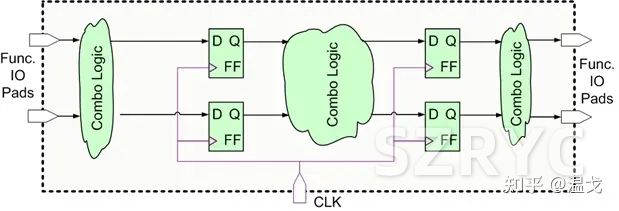

上面的兩幅圖都只有時序單元,我們再把組合邏輯放進來。

Before scan

After scan insertion

Scan test 的步驟:

1.把Scan-En設成0,此時電路工作在正常狀態(function mode)下, scan insertion對電路的正常功能沒有影響。

2.把Scan-En設成1,然后把enable clock來驅動寄存器,在Scan-In端輸入測試數據,然后在輸出端Scan-Out觀測,用此種方法便可以測試Flip-Flop.

3.測試組合邏輯的時候,把Scan-En設成1,然后enable clock來驅動寄存器,在Scan-In端輸入測試數據,兩個時鐘周期后,數據便會送到組合邏輯的輸入端。

4.然后把Scan-En設成0,時鐘打一拍,經過組合邏輯的輸出值便會送到右側的寄存器中。

5.再把Scan-En設成1,此時scan chain 工作在shift mode,此時便可以把組合邏輯的輸出值shift出來,和期望值進行比較。

經過這樣一個周期,圖中的組合邏輯和時序邏輯便都被測試到了。

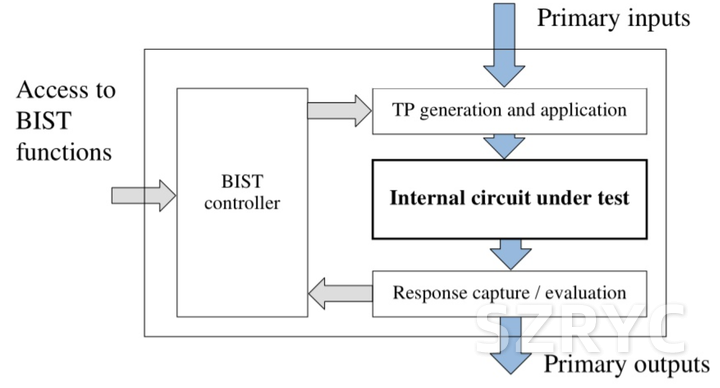

BIST -- 內建自測試

內建自測試(BIST)設計技術通過在芯片的設計中加入一些額外的自測試電路,測試時只需要從外部施加必要的控制信號,通過運行內建的自測試硬件和軟件,檢查被測電路的缺陷或故障。和掃描設計不同的是,內建自測試的測試向量一般是內部生成的,而不是外部輸入的。內建自測試可以簡化測試步驟,而且無需昂貴的測試儀器和設備(如ATE設備),但它增加了芯片設計的復雜性。

BIST大致可分為兩類:Logic?BIST(LBIST)?和?Memory?BIST?(MBIST)

LBIST通常用于測試隨機邏輯電路,一般采用一個偽隨機測試圖形生成器來產生輸入測試圖形,應用于器件內部機制;而采用多輸入寄存器(MISR)作為獲得輸出信號產生器。MBIST只用于存儲器測試,典型的MBIST包含測試電路用于加載,讀取和比較測試圖形。目前存在幾種業界通用的MBIST算法,比如“March”,March-C,MATS+算法。

另一種比較少見的BIST稱為Array?BIST,它是MBIST的一種,專門用于嵌入式存儲器的自我測試。Analog?BIST,則用于模擬電路的自我測試。???BIST技術正成為高價ATE的替代方案,但是BIST技術目前還無法完全取代ATE,他們將在未來很長一段時間內共存。

Scan和BIST是芯片可測性設計中兩種非常重要的技術,也是一個DFT工程師必備的技能。